A doksi online olvasásához kérlek jelentkezz be!

A doksi online olvasásához kérlek jelentkezz be!

Nincs még értékelés. Legyél Te az első!

Tartalmi kivonat

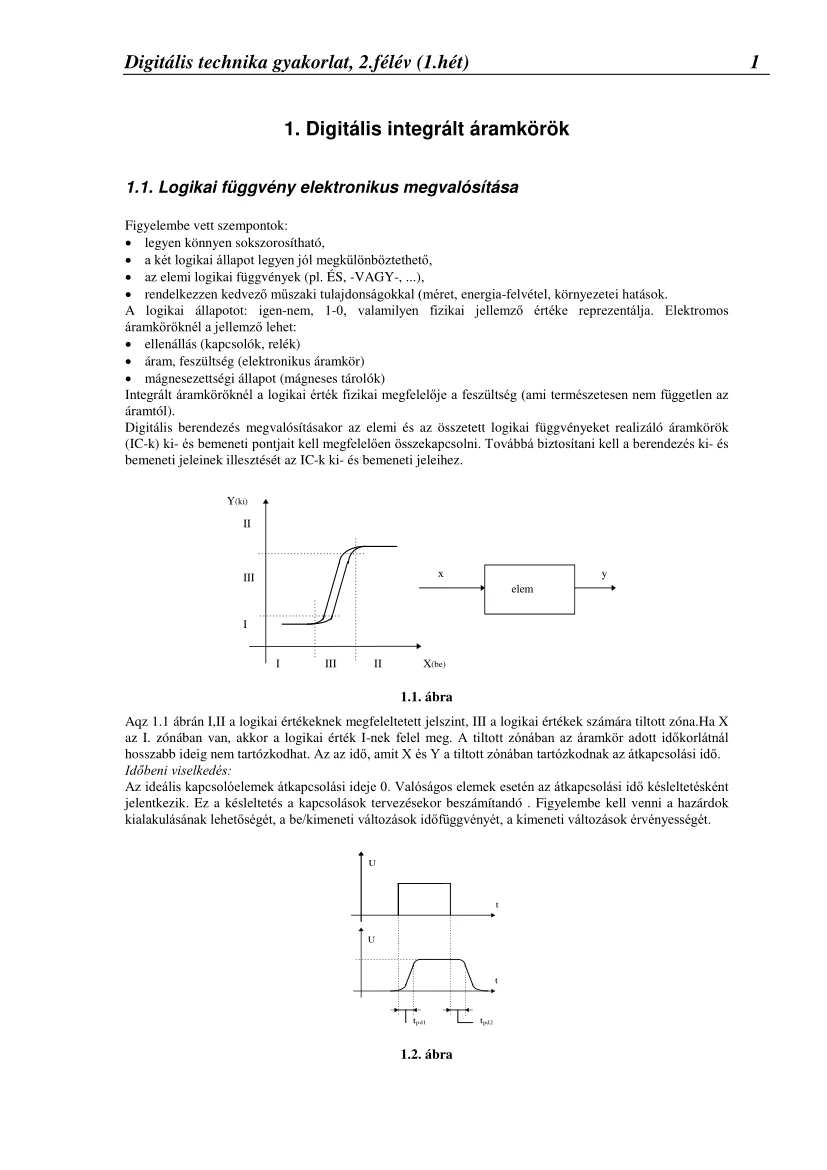

Digitális technika gyakorlat, 2.félév (1hét) 1 1. Digitális integrált áramkörök 1.1 Logikai függvény elektronikus megvalósítása Figyelembe vett szempontok: • legyen könnyen sokszorosítható, • a két logikai állapot legyen jól megkülönböztethető, • az elemi logikai függvények (pl. ÉS, -VAGY-, ), • rendelkezzen kedvező műszaki tulajdonságokkal (méret, energia-felvétel, környezetei hatások. A logikai állapotot: igen-nem, 1-0, valamilyen fizikai jellemző értéke reprezentálja. Elektromos áramköröknél a jellemző lehet: • ellenállás (kapcsolók, relék) • áram, feszültség (elektronikus áramkör) • mágnesezettségi állapot (mágneses tárolók) Integrált áramköröknél a logikai érték fizikai megfelelője a feszültség (ami természetesen nem független az áramtól). Digitális berendezés megvalósításakor az elemi és az összetett logikai függvényeket realizáló áramkörök (IC-k) ki- és bemeneti pontjait kell

megfelelően összekapcsolni. Továbbá biztosítani kell a berendezés ki- és bemeneti jeleinek illesztését az IC-k ki- és bemeneti jeleihez. Y(ki) II x III y elem I I III II X(be) 1.1 ábra Aqz 1.1 ábrán I,II a logikai értékeknek megfeleltetett jelszint, III a logikai értékek számára tiltott zónaHa X az I. zónában van, akkor a logikai érték I-nek felel meg A tiltott zónában az áramkör adott időkorlátnál hosszabb ideig nem tartózkodhat. Az az idő, amit X és Y a tiltott zónában tartózkodnak az átkapcsolási idő Időbeni viselkedés: Az ideális kapcsolóelemek átkapcsolási ideje 0. Valóságos elemek esetén az átkapcsolási idő késleltetésként jelentkezik. Ez a késleltetés a kapcsolások tervezésekor beszámítandó Figyelembe kell venni a hazárdok kialakulásának lehetőségét, a be/kimeneti változások időfüggvényét, a kimeneti változások érvényességét. U t U t tpd1 1.2 ábra tpd2 Digitális technika

gyakorlat, 2.félév (1hét) 1.2 Az integrált áramkörök jellemzői: a) Az áramkör logikai feladata, mely megadható . logikai egyenlettel táblázattal (igazságtábla, állapottábla, stb.) ütemdiagrammal b) Sebesség-időjellemzők úgy, mint. késleltetések jeltartási idők időkorlátok c) Teljesítmény jellemzők:. eldisszipált teljesítmény (Pd) d) Tápfeszültség jellemzők: . a tápfeszültség névleges értéke és toleranciája e) Logikai értékhatárok: a 0 vagy 1 logikai szintnek megfelelő, érvényesnek tekintett bemeneti és kimeneti feszültséghatárok, melyek a bemeneti és kimeneti minimum, maximum értékeket jelentik.( pl TTL esetben 1in=2.5V-5V, 1out=35V-5V és 0in=0V-08V, 0out=0V-04V) f)Terhelési és terhelhetőségi jellemzők:. kimeneti terhelhetőség FAN-OUT bemenetek fogyasztása (terhelés az előző fokozat számára) FAN-IN ezeket az értékeket sokszor egységértékben adják meg (pl.:FAN-OUT=10 TTL, azaz 10 TTL bemenetet tud meghajtani)

g) Hőmérsékleti jellemzők. üzemi hőmérséklettartomány tárolási hőmérséklettartomány h) Csatlakozási topológia, mely tartalmaz. tokozás IC lábkialakítás IC belső összeköttetéseire vonatkozó információt. Az áramkör-katalógusokban szereplő adatok a következő felosztásban szerepelnek: a) az áramkör meghibásodását még nem eredményező maximális értékhatárok (absolute maximum ratings), b) üzemi feltételek, az optimális üzemeltetéshez (recommended operating conditions) c) az üzemi feltételek betartása melletti jellemzők: minimum, tipikus, maximum értékek. A mai integrált áramkörök feszültséglogikával működnek. lásd pl logikai értékhatárok Az integrált áramkörök kimenete három kapcsolási alapkialakításra épül: • totem-pole • three-state • open-kollektor Az áramkörök általános leegyszerűsített kimeneti fokozata: + tápfeszültség R1 V1 K1 kimenet Uki, Iki V2 K2 R2 1.3 ábra ahol R1>>R2,

és K1, K2 félvezető eszközökkel megvalósított kapcsoló( kapcsolóüzemű tranzisztorok), amelyeket belső V1 és V2 vezérlőjelek vezérelnek (nyit-zár) Totem pole kimenet: Az áramkör belső V vezérlőjelével V=V1, -V=V2. A működés ily módon: a) K1 nyit, K2 zár,a kimeneten folyó Iki árammal a kimeneti feszültség: Uki=Iki⋅R2 a kimeneti áram nem lehet nagyobb, mint I kimax0 < U 0max R2 2 Digitális technika gyakorlat, 2.félév (1hét) ahol U0max a logikai 0 szint felső határa. b) K1 zár, K2 nyit U ki = U tá p − R 1 ⋅ I ki az előzőekhez hasonló határérték I kimax1 < U tá p - U 1min R1 ahol U1min a logikai 1 szint alsó határa . A totem-pole kimenet "ellenállásai" olyanok, hogy a kimenetek közvetlen összekötését nem viselik el. + U táp R1 K1 kimenet 1 kimenet 2 K2 R2 1.4 ábra Közvetlen összekötés esetén, ha a két jel eltérő logikai értékű (itt kimenet1='1', kimenet2='0') a 2.

kimeneten keresztül minimálisan Imin = U tá p R1 + R 2 áram folyik, amelyből Imin2*R1 és Imin2R1 teljesítményt el kell disszipálni. Ezt az áramkörök nem viselik el Three-state kimenet: K1 és K2 külön vezérelhetők. Működési fázisok: a) K1 és K2 nyitva van: a kimeneti pont belső meghajtás nélkül lebeg, tehát a vonal más kimenet által történő meghajtását teszi lehetővé. A helyes működés feltétele több kimenet összekötése esetén az, hogy a közvetlenül összekötött kimenetek közül egyidejűleg csak egynek lehet K1 kapcsolója zárt állapotban. Figyelembe kell venni azontúl, hogy a K1, K2 kapcsolók nem ideális kapcsolók, azaz kikapcsolt állapotban az impedanciájuk igen nagy, de nem végtelen. + Utáp R1 K1 kimenet Uki, Iki K2 R2 1.5 ábra b) Adott logikai szint előállításához a totem-pole kimenethez hasonlóan a K1 vagy a K2 kapcsoló van zárva a másik nyitva. 3 Digitális technika gyakorlat, 2.félév (1hét) 4

Nyitott kollektoros kimenet: Felépítésében a totem pole kimenettől annyiban tér el, hogy a K1 és R1 elemek elmaradnak kimenet Uki, Iki K R 1.6 ábra A V vezérlőjel aktív állapota a kimenet '0' szintjét biztosítja, a logikai '1' szint külső un. felhúzó ellenállással (Rc) biztosítható. Az Rc külső csatlakoztatása lehetővé teszi az ellenállás egyedi méretezését Így több open kollektoros kimenet közvetlen összekötésével huzalozott NOR kapcsolás hozható létre: • Rc-t mindig úgy kell méretezni, hogy ha minden kimenet K2 kapcsolója nyitva van, akkor a közös jel logikai '1' értékű legyen, • ha bármely, vagy több kimenet K2 kapcsolója zár, akkor a közös jel garantáltan logikai 0 legyen. Utáp A Rc 1.7 ábra A 1 0 B 1 0 C 1 0 X 0 0 0 1 X = A ⋅ B⋅C = A + B+ C Az Rc ellenállás méretezése: m db nyitott kollektoros kimenet van összekötve, a közös jel n kapubemenetet hajt meg, a közös

ellenálláson eső feszültség: U RC = I RC ⋅ R C ahol IRC az RC ellenálláson átfolyó áram, és az U X =U tá p-U RC feszültségnek a meghajtástól függően a '0' (0V.U0Lmax) logikai, vagy '1' (UOHminUtáp) logikai szintnek megfelelő feszültségsávba kell esnie: • U0Lmax a '0' szint maximális értéke • UOHmin az '1' szint minimális értéke Digitális technika gyakorlat, 2.félév (1hét) IRC Utáp Rc IOH IIH m kimenet n meghajtott bemenet 1.8 ábra ha minden kimenet '1' állapotban van, akkor az URC feszültségesés az RC ellenálláson nem lehet nagyobb, mint a logikai '1'-nek megfelelő feszültségsáv szélessége: ha ekkor egy bemeneten IIH (input-high) áramnak és egy kimeneten IOH (output-high) áramnak kell folynia U tá p - U OHmin ≥ R c I RC = (m ⋅ I OH + n ⋅ I IH ) RC maximális értékére: R Cmax ≤ U táp - U OHmin m ⋅ I OH + I IH n UOHmin, IOH, IIH az áramköri

technológiától függ, ha minden '1' állapotban, kivéve egyet, akkor a közös jelnek logikai '0'-nak kell lennie. IRC Utáp Rc n.IIL IIL IOL IIL m kimenet n meghajtott bemenet 1.9 ábra U tá p ≤ R C ⋅ I RC = R C ⋅ (I OLmax - n ⋅ I IL ) ha feltételezzük hogy csak egy kimenet akarja '0'-ba húzni a közös jelet (ha több, akkor a helyzet javul) és a közös pontra áramösszeget. RC minimumára a feltétel: R C min ≥ U tá p I OL - n ⋅ I IL az Rcmin és az Rcmax közötti ellenállásértékek közül választhatunk. 5 Digitális technika gyakorlat, 2.félév (2hét) 1 2. TTL flip-flopok alkalmazása Pergésmentesítés (A kapcsoló pergése esetén a kimenet csak egyszer vált) (S) K k1 Q k2 k1 S k2 R (R) Q 2.1 ábra Kétfázisú órajel előállítása Hazárd léphet fel. U F1 D Q Q 74 Clk F2 Q Cp Clk F1 F2 t 2.2/a ábra Helyes megoldás. U " 1" X F1 J Q Cp 76 Q K D Q74 Q 74 Cp Cp

F2 Q Q76 F1 F2 t 2.2/b ábra Mintavételezés D flip-floppal Közös órajellel vezérelt D flip-flop csoport alkalmas több bites adatvonalak állapotának adott pillanatban történő rögzítésére. X1 X1b D Q 74 Q Cp X2 X2b D Q 74 Q Cp X3 X3b D Q 74 Q Cp Xn Xnb D Q 74 Cp Q Cp 2.3 ábra Digitális technika gyakorlat, 2.félév (2hét) 2 Kettes osztó kialakítása JK flip-flop-ból: U X J Q Cp 76 Q K X Y X Y J Q Cp 76 Q K Y t 2.4 ábra Kettes osztó kialakítása D flip-flop-ból: U D X Y Q 74 X Q Cp Y t 2.5 ábra Flip-flop-ok átalakítása : T Cp D Cp J Q Cp 76 Q K J Q Cp 76 Q K 2.6 ábra T T D 74 Cp 1 Q Q Cp 1 Q D = TQ +TQ = T + Q 2.7 ábra J 1 J K D Q 74 Cp Cp 1 Q 1 1 Q K D = J Q + KQ 2.8 ábra Digitális technika gyakorlat, 2.félév (2hét) 3 Shiftregiszter kialakítása flip-flopokból: X be Pr J Cp Q Pr J Pr J Q J Q X be= 1 Pr Q Cp 76 Cp 76 Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q K

Clr Q Pr Pr Clear 0000 1000 1100 1110 1111 1111 a.) X be Pr J Cp Q Pr J J Q J Q Q Cp 76 Cp 76 Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q K Clr Q Load X be= 0 Visszacsatolva: 1000 0100 0010 0001 0000 0000 1000 0100 0010 0001 1000 0100 b.) 2.9 ábra Példa 2.1: Készítsen soros-párhuzamos átalakító áramkört, amely egy Start impulzust követő 4 db órajel alatt az Xbe bemeneten érkező jeleket fogadja és Strobe jel hatására párhuzamosan megjeleníti, az Y1(Start jel után az első órajel alatt beérkező Xbe érték), Y2, Y3, Y4 kimeneteken a kővetkező Strobe jelig. A Start jelet követően mindig van minimum 4 db. órajel a Strobe impulzusig A Start és Strobe jelek szinkronizáltak, egy órajel ideig tartanak, és nem fedhetik át egymást. Xbe bemenet értéke az órajel alatt ("1") nem változik U X be Y2 Y1 Y3 Y4 Clk Star t Str obe Q FF t 2.10 ábra Megoldás 2.1/1: D Q Y4 74 J " 1" Star t Q Cp X be J Pr Q Cp

76 Q K Q FF Pr Q J Pr Q J Pr Q J Pr Q Cp 76 Cp 76 Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q K Clr Q D Q Y3 74 Q Cp D Q Y2 74 Clr Q Cp D Clk Q 74 J Pr Q J Pr Q J Pr Q J Pr Q Cp 76 Cp 76 Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q K Clr Q Str obe 2.11 ábra Cp Q Y1 Digitális technika gyakorlat, 2.félév (2hét) 4 Megoldás 2.1/2: D Q Y4 74 Q Cp X be J " 1" Star t Pr J Pr Q Q FF Pr J Q Pr J Q Pr J Q D Q Cp 76 Cp 76 Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q K Clr Q Q Y3 74 Q Cp D Cp 76 Q Y2 74 K Clr Q Q Cp D Clk Q 74 J Pr Q J Pr J Q Pr Q J Pr Q Cp 76 Cp 76 Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q K Clr Q Str obe 2.12 ábra Cp Q Y1 Digitális technika gyakorlat, 2.félév (3hét) 1 3.Számlálók 3.1 Számlálók osztályozása Működés módja szerint: • aszinkron (soros, ripple), • szinkron. Számlálás iránya szerint: • egyirányú, • kétirányú (reverzibilis).

Kezdeti érték beállítása szerint: • nullázás (törlés/clear) Szinkron/aszinkron • induló érték megadása (töltés/load) Szinkron/aszinkron 3.2 Aszinkron számlálók (7490, 92, 93) SN7493, aszinkron bináris számláló QB QA H H Pr J A B Pr J Q Pr Cp 76 Cp 76 K Clr Q K Clr Q K Clr Q R1 J Pr Q Cp 76 Q K Q Cp 76 1:2 QD H H J Q QC Clr 1:8 R2 3.1 ábra Osztás: 1:2 az A bemenetre nézve; 1:2, 1:4 és 1:8 a B bemenetre. Számlálás az órajel lefutó órajelénél, törlés R1=R2=H esetén. Bővítés: f ki = f be /256 QA Q B Q C QD QA Q B Q C QD 7493 7493 f be A B A R1 R2 B R1 R2 L L 3.2 ábra A maximális bemeneti frekvencia a fokozatszám függvényében lényegesen csökkenhet. Számlálási ciklus rövidítése: átalakítás pl. decimális (0-9) számlálóvá: Hazár d kialakulása lehetséges ! QA Q B Q C QD 7493 f be A B R1 R2 3.3 ábra Ált.: 0-N-ig számol, N+1 állapotban töröl (rövid ideig N+1 is megjelenik)

Problémák: Digitális technika gyakorlat, 2.félév (3hét) 2 • A törlés idejére megjelenő N+1 értéket a kimenet megfelelő mintavételezésével ki kell szűrni. • A törlést végző impulzus szélessége nem meghatározott (bizonytalan törlés esetén nem mindegyik flipflop törlődik). SN7490, aszinkron BCD számláló Egy 1:2 és egy 1:5 osztófokozatból felépített számláló, QA és B összekötésével BCD-számlálóvá alakítható. Törlőbemenetek (4 db): R01, R02, R91, R92. Beállítás: R01 H H - R02 R91 R92 H H L L H - L H L QA L L H QB QC L L L L L L számlál QD L L H SN7492, aszinkron 0-11 számláló (1:2, 1:6, 1:12 osztás) 3.3 Szinkron számlálók (74160, 161, 162, 163) SN74160, szinkron BCD, szinkron beírás, aszinkron törlés SN74162, szinkron BCD, szinkron beírás, szinkron törlés SN74161, szinkron bináris, szinkron beírás, aszinkron törlés SN74163, szinkron bináris, szinkron beírás, szinkron törlés Beíró (LOAD),

törlő (CLR) és két engedélyező (ENP és ENT) jel, átvitel (RCO) kimenettel. LOAD QA Q CLR B Q C Q ENP ENT A B D RCO 74160-163 CLK C D Számlálás engedélyezés ENP QD QC QB QA ENT RCO engedélyezés RCO 3.6 ábra Az RCO kimenetekre alapozva a következően bővíthetőek: LOAD CLR ENP CLK " H" Q Q Q Q A B C D 74160-163 CLK ENT A B C LOAD RCO CLK D ENP CLR Q A Q B Q C 74160-163 ENT A B C Q D LOAD RCO CLK D ENP CLR Q Q Q Q A B C D 74160-163 ENT A B C LOAD RCO CLK D ENP CLR Q Q Q Q A B C D 74160-163 ENT A B RCO C D " H" 3.7 ábra Elnevezés: Carry Look-Ahead (Átvitelképzés gyorsítása, az alacsonyabb helyiértéken megjelenő átvitel felléptekor nem kell kivárni, míg az sorosan végigterjed a magasabb helyiértékeken.) Digitális technika gyakorlat, 2.félév (3hét) 3 Számlálási ciklus rövidítése: N-nel osztó elrendezés (pl. N=13): (A számláló tehát nem

nullától számol) ABCD LOAD A Q B Q C ENT A " H" Q D RCO 74163 CLK ENP Q CLR B C Count D " H" 0000 1000 0100 1100 0010 : Load 1111 " L" 3.8 ábra Számlálási ciklus rövidítése szinron törléssel (0-12-ig számláló): Szinkr on tör lés ABCD LOAD A Q B Q C ENT A Q D RCO 74163 CLK ENP Q CLR B C Count D 0000 1000 0100 1100 0010 : Clear 0011 3.9 ábra Számlálási ciklus rövidítése aszinron törléssel(0-12-ig számláló): Hazár dmentes megoldás ! Hazár d kialakulása lehetséges ! Szinkr on beír ás ABCD Aszinkr on tör lés ABCD LOAD CLR B Q C ENT A Q D RCO 74161 CLK ENP QA Q B C Count D 0000 1000 0100 1100 0010 : LOAD Clear Q A Q B Q C ENP ENT " H" A Q D RCO 74161 CLK 1011 " H" CLR B C D " L" Count 0000 1000 0100 1100 0010 : Load 0011 3.10 ábra SN74190, szinkron BCD, aszinkron beírás, előre/hátra léptetés.

SN74191, szinkron bináris, aszinkron beírás, előre/hátra léptetés. Beíró (LOAD), engedélyező (CTEN), számlálási irány meghatározó (D/U) bemenetekkel és két átvitel (RCO és MAX/MIN) kimenetekkel. Az U/D és CTEN változása csak CLK = H alatt engedélyezett LOAD CLK CTEN D/U QA Q B 74190-191 A B Q C Q D MAX/MIN C RCO D 3.11 ábra Példa 3.1: N1-től N2-ig N3-tól N4-ig számláló eszköz tervezése SN74163 felhasználásával (N1=21, N2=39, N3=72, N4=101). Megoldás 3.1: Digitális technika gyakorlat, 2.félév (3hét) 2 4 0 2 4 39 101 LOAD CLR A Q Q B C ENP ENT " H" Q LOAD D RCO 74163 CLK Cp Q A B C D " H" " L" " H" " L" QA Q CLR Q B Q C ENP ENT A D RCO 74163 CLK B C D " H" ABCD ABCD Count 1010 : 1110 1000 : 0100 Count 0001 : 1010 0010 : 0110 21: 39: 72: 101: 2 0 2 " L" " L" Load 7 3.12 ábra Példa 3.2:

Reverzibilis, 20 és 63 között számláló eszköz tervezése SN74190 felhasználásával Megoldás 3.2: 2 0 2 0 21 62 Load x1 QA Q LOAD B CTEN D/U A C Q x10 QA Q LOAD D MAX/MIN 74190 CLK Q B C RCO D J Pr Q Cp 111 K Clr Q 21: Count 62: Q CTEN D/U C Q A B RCO D C " L" ABCD ABCD 1000 : 0100 BCDx1 0010 : 0110 BCDx10 " H" CLK 61 22 Count D MAX/MIN 74190 CLK " L" CLK B 62 21 63 20 Q111 Flip-flop mintavétel 3.13 ábra Házi feladat: Az alábbi számsorozatot ciklikusan előállító bináris számláló megtervezése: 30, 32, 34, . 66, 77, 79, 81, 101, 100, 99, 98, 97, , 33, 32, 31 62 21 Digitális technika gyakorlat, 2.félév (4hét) 1 4. Aritmetikai áramkörök SN 74181 Aritmetikai-logikai egység (ALU) AKTIV-LOW DATA AKTIV-HIGH DATA S3 S3 S2 S1 S0 ALU S2 S1 S0 P M A3 A2 Cn+4 Cn+4 F3 F2 B1 F1 SN74181 Y B3 B2 F2 B0 Cn F0 A=B X A1 A0 F3 B3 B2 B1 ALU M A3 A2 G A1 A0

B0 Cn A=B F1 SN74181 F0 4.1 ábra Kiválasztás S3 S2 S1 S0 L L L L L L L H L L H L L L H H L H L L L H L H L H H L L H H H H L L L H L L H H L H L H L H H H H L L H H L H H H H L H H H H M = H; Logikai műveletek F=A F = AB F=A+B F=1 F=A+B F=B F=A+B F=A+B F = AB F=A+B F=B F=A+B F=0 F = AB F = AB F=A ACTIVE-LOW DATA. M = L; Aritmetikai műveletek. Cn =L Cn = H (no carry) (with carry) F = A MINUS 1 F=A F = AB MINUS 1 F = AB F = AB MINUS 1 F = AB F = MINUS 1 (2’s kompl.) F = ZERO F = A PLUS (A + B) F = A PLUS (A + B) PLUS 1 F = AB PLUS (A + B) F = AB PLUS (A + B) PLUS 1 F = A MINUS B MINUS 1 F = A MINUS B F=A+B F = (A + B) PLUS 1 F = A PLUS (A + B) F = A PLUS (A + B) PLUS 1 F = A PLUS B F = A PLUS B PLUS 1 F = AB PLUS (A + B) F = AB PLUS (A + B) PLUS 1 F=A+B F = (A + B) PLUS 1 F = A PLUS A* F = A PLUS A* PLUS 1 F = AB PLUS A F = AB PLUS A PLUS 1 F = AB PLUS A F = AB PLUS A PLUS 1 F=A F = A PLUS 1 A 74181 két 4-bites bemenet (A0.A3, B0B3) között létesít

függvénykapcsolatot kimenete (F0F3) felé, ahol a függvényt 4+1-bites vezérlő bemenet (S0.S3 és M) választja ki A megvalósított logikai függvények többek között logikai és aritmetikai függvények vannak a fenti táblázat szerint. Az aritmetikai egységek kaszkádosítása a C0 bemenet a Cn+4, P és G kimenetekkel lehetséges. Aktív HIGH DATA duálja az aktív LOW DATA-nak. Pl.: S3,S2,S1,S, M: L,L,LH, H F = A+B Digitális technika gyakorlat, 2. félév(4hét) - Aritmetikai áramkörök 2 SN74182 Gyorsvitelképző G2 P2 Cn+z G1 P1 Cn+y G0 P0 Cn+x Cn G3 P3 SN 74182 P G 4.2 ábra Példa 4.1: Készítsen 32 bites, gyors átvitellel rendelkező aritmetikai egységet SN 74181-es és SN 74182-es áramkörök alkalmazásával! Megoldás 4.1: SN 74181-es ALU ár amkör ök A 0.3 B 03 A 4.7 B 47 A 8.11 B811 A12.15 B1215 A16.19 B1619 A 20.23 B 2023 A 24.27 B2427 A28.31 B2831 Cn Cn Cn Cn Cn Cn Cn Cn G P G0 P0 Cn+x Cn G P G1 P1 Cn+y G P G2 P2 Cn+z

SN 74182 G P G3 P3 G G P G0 P0 Cn+x Cn P G1 P1 Cn+y G P G2 P2 Cn+z SN 74182 Cn G P G3 P3 G P G P G0 P0 Cn G1 P1 Cn+y G0 P0 Cn+x Cn Cn G P SN 74182 4.3 ábra A 74182 áramkörök a 4.3 ábrának szerint kaszkádosíthatók, a G és P be/kimeneteik felhasználásával Példa 4.2: Tervezzen logikai hálózatot, amely két 7 bites, bináris, előjeles, kettes komplemensű számra (x0x7, y0.y7) előállítja a 4*(x-y) művelet eredményét kettes komplemens kódban. A két operandus 2 lépésben, a START impulzus alatti és az azt követő órajelimpulzussal ütemezve, negáltan érkezik az XA.XD, YAYD bemenetekre a 4.4 ábra szerint A negált eredmény a következő START impulzusig álljon rendelkezésre Használja fel a 74LS181 tip. ALU áramkört A két operandusra és az eredményre az x0, y0, E0 a legalacsonyabb helyiérték. A ciklus első CLK impulzusa mindig a START alatt érkezik Két START impulzus között legalább 3 órajel van. START Clk XA.XD LH YA.YD

Clk START XA.XD x4,x5 x6,x7 YA.YD y4,y5 y6,y7 E0.E10 E0.E10 4.4 ábra x0,x1 x2,x3 y0,y1 y2,y3 Digitális technika gyakorlat, 2. félév(4hét) - Aritmetikai áramkörök Megoldás 4.2/1: 74125 74374 XA.XD 1Q-4Q 1D-4D 74181 A C n+4 F YA.YD 5Q-8Q 5D-8D * B 1G Cn S M M=L S0 = L S1 = H S2 = H S3 = L CLK OC E10 A Y 74LS244 1A * YY E2.E9 2A A 74374 1Q-4Q 1D-4D 74181 A C n+4 1G 2G E1 E0 F 5Q-8Q 5D-8D B Cn S M M=L S0 = L S1 = H S2 = H S3 = L CLK OC START D 74 Cp Cp D Q 74 Q Q Q Cp 4.5 ábra Megoldás 4.2/2: 74374 74374 XA.XD 74181 1Q-4Q 1D-4D A C n+4 1Q-4Q E10 1D-4D F YA.YD 5Q-8Q 5D-8D B Cn S CLK OC M CLK OC M=L S0 = L S1 = H S2 = H S3 = L 74374 1Q-4Q 1D-4D E2.E9 5Q-8Q 5D-8D 74181 A C n+4 F B Cn S M=L S0 = L S1 = H S2 = H S3 = L START D 74 Cp M Cp Q D Q Cp 74 Q Q 4.6 ábra CLK OC E1 E0 3 Digitális technika gyakorlat, 2.félév (5hét) 1 5. Komparátorok SN7485: 4 bites komparátor (megj.: eltérés az L és a

többi sorozat lábkiosztásában!) A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 A<B A=B A>B 5.1 ábra Működés: a kimenetek értéke a 4-4 adatbit alapján dől el, ha a két bemeneten érkező kombináció nem azonos, ellenkező esetben a komparátor a bejövő relációbitek (IN) értékét másolja ki a kimenetre. (Akkor is, ha a kaszkád bemeneten érvénytelen a bemeneti kombináció, pl. A<B és A>B egyidejűleg magas szintű)16 bites komparátort soros kaszkádosítással az 5.2 ábra szerint lehet összeállítani A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 A<B A=B A>B A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 A<B A=B A>B A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 A<B A=B A>B A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 A<B A=B A>B 5.2 ábra A soros kaszkádosítás előnye, hogy a szintek számának növelésével az összehasonlítható értékek bitjeinek száma egyszerűen, korlát nélkül növelhető.

Példa 5.1: 16 bites, párhuzamos kaszkádosítással megvalósított komparátor áramkör felépítése 7485-s áramkörök felhasználásával. Megoldás 5.1: A párhuzamos kaszkádosítás azon alapul, hogy a sokbites számok egymáshoz viszonyíthatóak (esetünkben 4 bites) blokkjaik alapján, hiszen például A>B, ha (A15>B15) vagy (nem(A15<B15) és A14>B14) vagy (nem(A15<B15) és nem(A14<B14) és A13>B13) vagy . (nem(A15<A14) és . és nem(A1<B1) és A0>B0) A 4 bites komparátorok négy kifejezést képesek kiértékelni egyszerre, ekkor a hasonlítás tetrádok vizsgálatára bontható fel: A>B, ha (a3>b3) vagy (nem(a3<b3) és a2>b2) vagy (nem(a3<b3) és nem(a2<b2) és a1>b1) vagy (nem(a3<b3) és nem(a2<b2) és nem(a1<b1) és a0>b0), ahol a3, a2, a1, a0, b3, b2, b1, b0 rendre A illteve B 4 legmagasabb helyiértékű, . 4 legalacsonyabb helyiértékű bitjét jelenti (A15.A12, A11A8, A7A4, A3A0, B15B12,,B3B0) A

kifejezést ezek után egy újabb 4 bites komparátorral értékeltetjük ki (felhasználva, hogy a négy reláció kiértékelése gyakorlatilag újabb négybites értékek komparálását jelenti): Digitális technika gyakorlat, 2.félév (5hét) A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 A12.A15 A8.A11 B8.B11 A4.A7 B4.B7 A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 7485 B12.B15 2 7485 A>B A=B A<B A>B A=B A<B A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 A>B A=B A<B A3 A2 A1 A0 A<B A=B A>B B3 B2 B1 B0 A0.A3 B0.B3 7485 A>B A=B A<B 7485 A>B A=B A<B 5.3 ábra A megoldás előnye, hogy a komparátorokat csupán két szinten kapcsoljuk össze, így a kimenet megjelenéséig kevesebb idő telik el, mint a soros kaszkádosítás esetében. Időzítés: A kimenet beállásához szükséges időt az egymás után kapcsolt komparátorok száma határozza meg. Ez n darab sorba kapcsolt

komparátor esetén T=TAB + (n-1) * TK, ahol TAB az A és B bemenetektôl a kimenetig, TK a kaszkád (reláció) bemenetektől a kimenetig mérhető jelterjedési idő. Célszerű, ha TK<TAB SN74682: 8 bites komparátor (kaszkád bemenetek nélkül) Nagyobb bitszámú (8) értékek összehasonlítására alkalmas a 74682.689 csoport: 74682 A8 : : A0 A=B A>B B8 : : B0 5.4 ábra A 7485-nél elmondottaknak megfelelően felírhatóak a logikai függvények: bA = Bg= bA7 = B7gb ⋅ A6 = B6g ⋅K⋅b A0 = B0g bA > Bg= A7 ⋅ B7 + bA7 = B7g⋅ A6 ⋅ B6+K +bA7 = B7g⋅K⋅bA1= B1g⋅ A0 ⋅ B0 Közvetlen kaszkádosításra az áramkör nem alkalmas. Példa 5.2: Hasonlítson össze két 16 bites számot és valósítsa meg a hálózat relációkimeneteit két darab 74682 felhasználásával! Digitális technika gyakorlat, 2.félév (5hét) 3 Megoldás 5.2: (A=B)1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 (A>B)1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 A=B A>B (A=B)2 0 0 1 1 0 0 1 1 0

0 1 1 0 0 1 1 (A>B)2 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 A>B A<B 0 0 1 0 0 0 1 1 1 A>B 0 1 0 1 1 1 0 0 0 A=B 1 1 A=B 2 értelmetlen A>B 2 A>B 1 1 A=B 1 értelmetlen 1 A>B 1 1 Megjegyzés értelmetlen értelmetlen értelmetlen értelmetlen értelmetlen A<B 2 1 A>B A=B A>B 2 1 A=B A=B 1 0 0 0 0 0 0 0 0 1 1 1 1 1 A=B 2 2 5.5 ábra bA = Bg= bA = Bgb ⋅ A = Bg, (A > B) = (A > B) + (A = B) ⋅ (A > B) 1 1 2 1 2 (A < B) = (A = B)1 ⋅ (A > B)1 + (A > B)1 ⋅ (A = B) 2 ⋅ (A > B) 2 = (A > B) ⋅ (A = B) A15 : : A8 74682 B15 : : B8 A>B A7 : : A0 74682 A=B A=B A = B1 A>B A<B A=B A>B A = B2 B7 : : B0 5.6 ábra Példa 5.3: Készítsen 15 bites komparátort kaszkádosított 74682-s IC-k felhasználásával! Megoldás 5.3: Mivel a 74682 nem rendelkezik közvetlen kaszkádbemenettel, valamelyik (a legalacsonyabb helyiértékű) adatbiten kell beadni az első komparátor kimenetét.

A második komparátor A0 és B0 bitjeire tehát az alábbi értékek kerülnek: (A=B)1 (A>B)1 A02 B02 Megjegyzés 0 0 1 1 0 1 0 1 0 1 0/1* - 1 0 0/1* - A1<B1 A1>B1 A1=B1 ellentmondás Digitális technika gyakorlat, 2.félév (5hét) 4 A *-gal jelölt esetben a választás tetszőleges, de a két értéknek meg kell egyeznie. Ha mindkét értéket 1-re választjuk, a függvények a következőképpen valósíthatóak meg: bA 0 g= bA = Bgb B0 g =b A > Bg. ⋅ A > Bg, b 2 2 1 1 A7 :: A0 74682 1 A megvalósított 15 bites komparátor tehát a következőképpen néz ki: A14 :: A8 A=B A>B 74682 A=B A=B B14 :: B8 B7 :: B0 A>B A>B A<B 5.7 ábra Paritásgenerálás és ellenőrzés SN74180: 8/9 bites paritásgenerátor és paritásellenőrző. Bemenetek: 8 darab adatbit (X), páros/páratlan bitek (Even In (EI), Odd In (OI)) Kimenetek: Páros/páratlan bitek (Even Out (EO), Odd Out (OO)) A.H-n belüli egyesek száma páros páratlan

páros páratlan - EI 1 1 0 0 1 0 OI 0 0 1 1 1 0 EO 1 0 0 1 0 1 OO 0 1 1 0 0 1 Paritásgenerátorként tehát a 74180 az EI/OI magas állapota mellett az adatbiteket páros és páratlan paritásúra egészíti ki az OO/EO és az EO/OO kimeneteken. Paritásellenőrzéskor a kilencedik adatbitet az EI-re, negáltját az OI-re vezetve páros/páratlan paritást feltételezve az EO/OO magas szintje paritáshibát jelez. Nyocbites paritás-generátor 74180 A : H EVEN EVEN 74180 A : H EVEN EVEN ODD ODD ODD ODD Páros paritás-generátor Páratlan paritás-generátor 5.8 ábra Digitális technika gyakorlat, 2.félév (5hét) 5 Kilencbites paritás-generátor 74180 A : H 74180 A : H EVEN EVEN I EVEN EVEN ODD I ODD ODD ODD Páros paritás-generátor Páratlan paritás-generátor 5.9 ábra Paritás-ellenörzés 74180 A : H Error (even) EVEN P EVEN ODD 5.10 ábra Error (odd) ODD Digitális technika gyakorlat, 2.félév (6-7hét) 1 6-7. Memória

illesztése mikroprocesszorhoz 245 -OE ADAT MEMÓRIA DIR -G2 -WR -CS 244 CIM címdekóder -G1 -G2 MIKRO PROCESSZOR 244 írás/ olvasás vezérlés VEZÉRLÉS -G1 -G2 READY RDY -RDY 6.1 ábra Adatmeghajtó: Célrendszereknél esetfüggően alkalmazva, buszok esetén minden esetben használatos. DIR vezérlés kérdései (van-e mögötte is olvasható eszköz), általában az olvasás vezérlőjel hajtja meg, G-t általában a HOLD állapot jelzése vezérli, buszrendszerek esetén a slave kártyákon is van. G = CIMazonosság ∗ parancsazonosság Címmeghajtó: Célrendszerek esetén a kapacitív és az egyenáramú terhelések alapján mérlegelendő az alkalmazásuk buszrendszereknél minden esetben kell. Ready: Sebesség szinkronizálására. Hibajelző képesség watch dog. Ready stratégiák: a) nem kell (mindig kész) b) ott kell, ahol lassú (itt WAIT-et kér) c) mindig kell (ready-t ad) 1. Időzítési viszonyok a processzor szempontjából T1 T2 TW T3 CLK

A8.15 AD0.7 address address data in data stable ALE A cím latchelése után az AD0.7 vonalak vezérelve vannak ↓ -RD -READY 110ns i8085 IO/-M 6.2 ábra Tipikus olvasási ciklus csak a -RD jel aktíválása után vezérelhető az adatbusz Digitális technika gyakorlat, 2.félév (6-7hét) T1 T2 2 T3 CLK A8.15 address AD0.7 address Csak -WR aktív esetén érvényes az adat. A -WR hiánya nem jelenti az olvasás engedélyezését. data out ALE ↓ tDSU olyan RAM-ot, ahol nincs -OE, ott le kell válysztani, vagy -CS-be -RD-t és WR-t bele kell kapuzni -WR IO/-M 6.3 ábra Tipikus írási ciklus 2. Időzítési viszonyok a memóriaelemek szempontjából − konkrét típusok kapcsán Memóriák: RAM (statikus, dinamikus), ROM, PROM, EPROM, EEPROM i2764 8kb EPROM tipikus olvasási ciklus A0.A12 D0.D7 A0.A12 CE CE CE t OE OE OE stabil t i2764 érvényes D0.D7 6.4 ábra TC5516 2kb statikus RAM t A0.A10 ACC t CE1 D0.D7 TC5516 t AW min 0ns

CE1 t CE2 t R/W t WP DS DH min 200ns min 120ns min 0ns t CE2 t COE t OD t OH max 250ns max 100ns max 250ns min 10ns max 80ns min 10ns Digitális technika gyakorlat, 2.félév (6-7hét) 3 tipikus írás ciklus stabil t A0.A10 AW t t WP COE CE1 CE2 DH DS OD érvényes bemenet D0.D7 kimenet! tipikus olvasás t t t R/W t ACC stabil A0.A10 t CE1 CE1 t CE2 CE2 t R/W OD D0.D7 érvényes t t COE OH korai jellel vezérelt írási ciklus (egyáltalán nem hajt az adatbuszra) stabil A0.A10 CE1 CE2 R/W D0.D7 érvényes bemenet 6.5 ábra CS, CE: OE: R/W: a chip-ek működésének engedélyezése, címdekódoló generálja a kimeneti erősítők működésének engedélyezése, írás-olvasás vezérlő generálja (tipikusan az RD jel) beírás engedélyezése, írás-olvasás vezérlő generálja (tipikusan a WR jel) 3. Alapvető illesztés 15 0 n bit A0.A12 -WR m bit RAM Memória térkép: R/-W -CS 0000 8k * m A13.A15 cím

D0.D7 -READY 2 8k cím dekóder 2n blokk -IO/M 8k címdekódolás: 74LS138, i8205, PROM, PLA, komparátor (ha nem használom a teljes címtartományt, akkor nem is kell teljes dekódolás!) 6.6 ábra Digitális technika gyakorlat, 2.félév (6-7hét) 4 4. Ha a memória adatszélessége keskenyebb (pl 1bites RAM) A0.Ax RAM RAM R/-W -CS R/-W -CS RAM R/-W -CS -WR -CS D1 D0 D7 6.7 ábra 5. MSI elemkészlet Tervezés során csak létező elemeket használjunk.(pl: nincs 7 bemenetű NAND kapu) Elemkészlet: Sorozat: Belső elemszám: Funkció: 74LS00 74LS02 74LS04 7406 7407 74LS08 74LS21 74LS32 74LS244 74LS245 74LS373 4 4 6 6 6 4 2 4 2x4 1x8 1x8 2 bemenetű NAND 2 bemenetű NOR invereter OC inverter OC meghajtó 2 bemenetű AND 4 bemenetű AND 2 bemenetű OR TRI STATE meghajtó kétirányú TRI STATE meghajtó DG flip-flop Példa 6.1: 2 db 2764 EPROM és 1 db 5564 statikus RAM illesztése 8085 processzorhoz. Memóriakiosztás: EPROM1:

RAM: EPROM2: C000h.D7FFh D800h.E7FFh E800h.FFFFh (6kb!) (6kb!) Busz: A0.A15 D0.D7 címbusz (a címtárolás megtörtént) adatbusz SRAM: nincs -OE vezérlőláb − megoldási lehetőségek: -RD és -WR bele van kapuzva a RAM engedélyezésébe (vö.: korai jellel vezérelt írás) leválasztó buffert alkalmazunk az adatbuszon (‘244/’245) Megoldás 6.1: A ⋅A ⋅ IO / M = CS 15 1. a felső 16 kB 14 , 2. a dekódolt 16kB-ot 8 db 2 kB-os blokkra osztjuk, majd ebből: • az első 3 EPROM • a második 2 RAM Digitális technika gyakorlat, 2.félév (6-7hét) 5 • a harmadik 3 EPROM 3. 74LS245 irányát -RD adja meg, 4. 74LS245 engedélyezése -G = -RD ∗ -WR + -CS, 5. a buszon csak egységnyi terhelés lehet, ezért 74LS244, 74LS32, 74LS04 áramköröket mint meghajtót alkalmazunk. Digitális technika gyakorlat, 2.félév (6-7hét) 6 74LS32 244 -RD 2764 A0.A15 -OE A0.A12 -G1 -G2 74LS21 D0.D7 -CS 74LS138 2764 -OE A0.A12 -G1 -G2 D0.D7 -CS IO/M 2x74LS04

74LS21 2x74LS08 A14 5564 245 D0.D7 A11 A12 A13 -Y0 A -Y1 B -Y2 C -Y3 -Y4 -Y5 -E1 -Y6 -E2 -Y7 E3 244 -WR A0.A12 74LS08 7406 (OC) A15 DIR -G2 D0.D7 -CE1,-CE2 -WR 74LS08 74LS08 74LS32 74LS32 6.8 ábra Példa 6.2: 1 db 27128 EPROM és 1 db 5564 statikus RAM illesztése 8085 processzorhoz. Megoldás 6.2: Memóriakiosztás: EPROM: 0000h.3FFFh nem teljesen dekódolva RAM: E000h.FFFFh Ha a -CS függvénye a -WD,-RD-nek, az kedvezőtlenebb, mint a -OE vagy a leválasztás, mert a -CS-re lassabban reagál a RAM. A -READY jeleknél fontos az időzítés, különben felesleges wait ciklusokat rakunk a memória kezelésébe. Előfordulhat, hogy az ALE lefutása után már kevés az idő a -READY kialakulására, ezért nem mindig lehet élvezérelt latchet alkalmazni. Nem teljesen dekódolt megoldás alsó 32kB RAM felső 32kB ROM LS 245-ös engedélyezése minden memória írásra, olvasásra megtörténik, minden memória olvasásra, írásra van READY is. Digitális technika

gyakorlat, 2.félév (6-7hét) 244 7 27128 -OE A0.A13 A0.A15 -G1 -G2 D0.D7 -CS A15 244 5564 -WR A0.A12 -G1 -G2 D0.D7 -CS D0.D7 245 A15 * -READY -WR DIR -G2 -MRD*-MWR IO/-M -MRD -RD 74LS08 74LS32 6.9 ábra Példa 6.3: RAM számára 0, EPROM számára 0.7 wait-et beiktató READY logika tervezése Megoldás 6.3: általános megjegyzések: lefelé él után nincs biztosítva elég idő a READY-hez pl.: 8085 felfutó órajel előtt legalább 110 ns a -RD és a -WR jel figyelembe vétele legalább 1 wait-et jelent -CSRAM * -READY * A B CLK Qa Qb Qc Qh ‘164 CK -CLR -CSEPROM -RD -WR T1 T2 TW1 CLK ALE -READY CSEPROM (A,B) Qa Qb 6.10 ábra TW2 T3 Digitális technika gyakorlat, 2.félév (8hét) 1 8. SID, SOD vonalak alkalmazása 0. RIM utasítás A: RST 5.5 beállított maszk ( "1" maszkolt) RST 6.5 beállított maszk RST 7.5 beállított maszk INTE ( megszakítás FF értéke) RST 5.5 bemenet értéke RST 6.5 bemenet értéke RST 7.5 bemenet

értéke SID bemenet értéke 0. SIM utasítás A: RST 5.5 maszk beállítás ( "1" maszkol) RST 6.5 maszk beállítás RST 7.5 maszk beállítás Maszk beállítás engedélyezés RST 7.5 megszakítás FF törlése SOD állítás engedélyezés SOD kimenet 8.1 ábra Példa 8.1: A 81 ábra szerint egy i8085-ös processzor SID bemenetére pergésmentesített kapcsolót kötöttekA SOD kimenetről egy LED diódát lehet vezérelni. A processzoron futó programnak a SID bemenetre érkező jeleket kell figyelnie és ez alapján vezérelni a LED diódát. A bekapcsolás után a SID bemenetre érkező jel első felfutó élre a diódának világítani kell, a bemenetre érkező következő impulzus lefutó élére pedig el kell aludnia (8.2 ábra) Készítsen el egy olyan assambly programot, amely ezt a vezérlést ciklikusan ismétli Aprogram címe legyen 8000H. SID t SOD t C: 0 1 2 0 8.2 ábra i8085 i8085 sín SID Q S R SOD 8.3 ábra Megoldás 8.1: A programban

alkalmazott regiszterek feladata: B: Előző mintavételezéskor a SID bemenet értéke, C: Ciklus állapot-tárolója, D: Aktuális SID érték nyomógomb Digitális technika gyakorlat, 2.félév (8hét) 2 1 RIM B: = SID SOD = 0 C=0 RIM D: = SID NEM D XOR B = 1 ? nem (lefutó él) B=0? nem igen igen (felfutó él) B: = D B: = D C=2? C=0? igen igen nem SOD = 1 C: = C+1 8.4 ábra ORG 8000H KEZD: RIM ANI 80H MOV B,A ;------------------------------------------------------------------FOCIKL: MVI A,40H SIM MVI C,00H ;STATUS:=0 ;-----------------------------------------------------------------------CIKL1: RIM ANI 80H ;FELSO BITRE MASZK MOV D,A ;UJ ERTEK MENTESE XRA B ;A XOR B, FIGYEL JZ CIKL1 ;UGRIK, HA SID NEM VALTOZOTT XRA A ;A:=0 ORA B ;0+B JZ FELFUT ;UGRIK, HA FELFUTÓ EL ;------------------------------------------------------------------------------LEFUT: MOV B,D ;REGI SID ERTEK FRISSITESE MOV A,C CPI 2 JZ FOCIKL ;UGRIK, HOGY SOD LEESSEN JMP CIKL1

;--------------------------------------------------------------------------------FELFUT: MOV B,D ;REGI SID ERTEK FRISSITESE XRA A ORA C JNZ FEL1 ;UGRIK,HA NEM ELSO EL MVI A,0C0H SIM ;SOD=1 FEL1: INR C ;C:=C+1 JMP CIKL1 ;----------------------------------------------------------------------------------------END Példa 8.2: Mod 256-os számláló i8085-ös processzorral A processzor RST 55 bemenete a számláló engedélyező jele, és a SID bemenetre érkeznek az impulzusok. Az áramkör az impulzusok felfutó élére működjön mod. 256 számlálóként Az áramkör kimenete a processzor SOD kimenete, amelyen 256 impulzusonként egy ciklusidőre jelenik meg pozitiv impulzus. Az bemenő impulzusok szélessége nagyobb mint 0.5 ms és a két bemenet változása egymástól 50µs-nál nagyobb távolságra van Digitális technika gyakorlat, 2.félév (8hét) 3 1. SID 256. t nem számol számol RST 5.5 >50µs t SOD t 8.5 ábra i8085 i8085 sín SID Q S R Nyomógomb

SOD Q RST 5.5 S R Kapcsoló 8.6 ábra Megoldás 8.2/1: Az RST 5.5 vonal programozott lekérdezésével 1 RIM B: = SID SIM (SOD = 0) L=0 RIM E: = RST 5.5 D: = SID nem B: = D D XOR B = 1 ? igen nem (lefutó él) B=0? igen (felfutó él) nem E=1? igen L: = L-1 L=0? nem igen SIM (SOD = 1) 8.7 ábra A programban alkalmazott regiszterek feladatai: B: Előző mintavételi SID érték. SIM (SOD = 0) Digitális technika gyakorlat, 2.félév (8hét) 4 D: Aktuális SID érték. E: Aktuális RST 5.5 érték L: Számláló értéke. Egyidőben történik a mintavételezése a SID és RST 5.5 bemeneteknek, ezért a jelek elvileg egyidőben is változhatnak (az 50µs-os idő a két változás között nincs kihasználva). ORG 8000H ; INIC: RIM ANI 80H MOV B,A ;ELOZO SOD BEALLITASA A B-BE MVI A,4FH ;FELES IT-K TILTASA, SOD=0 SIM XRA A MOV L,A ;L=0 ;---------------------------------------------------------------------------------KEZD: RIM PUSH PSW ANI 10H MOV E,A ;E=RST 5.5 POP

PSW ANI 80H MOV D,A ;D=AKTUALIS SID XRA B ;VOLT SID VALTOZAS ? JZ KEZD ;UGRIK, HA NEM VOLT XRA A ORA B ;ELOZO SOD „0” VOLT ? JZ FELFUT ;URIK, HA FELFUTO EL ;------------------------------------------------------------------------------------LEFUT: MOV B,D ;ELOZO ERTEK FRISSITESE JMP KEZD ;----------------------------------------------------------------------------------------FELFUT: XRA A ORA E ;KELL SZAMOLNI? JZ LEFUT ;UGRIK, HA NEM KELL (RST 5.5=0) DCR L JNZ TORL ;UGRIK, HA NEM A256. IMP MVI A,0C0H ;SOD=1 PARANCS SZO SIM JMP LEFUT TORL: MVI A,40H ;SOD=0 PARANCS SZO SIM JMP LEFUT ;----------------------------------------------------------------------------------------END Megoldás8.2/2: RST 5.5 megszakításkérés alkalmazásával FÕPROGRAM RIM B: = SID SIM (SOD = 0) L=0 RIM D: = SID nem B: = D D XOR B = 1 ? igen nem (lefutó él) B=0? igen (felfutó él) Megszakítás engedélyezés RST 5.5 rutin L: = L-1 L=0? nem igen SIM (SOD = 1) Megszakítás tiltás RET SIM

(SOD = 0) Digitális technika gyakorlat, 2.félév (8hét) 5 8.8 ábra Az RST 5.5 megszakításkérő jel szintjére történik meg a szubrutin meghívása, akkor ha a SID vonal felfutó élére a megszakítások tiltása megszünik (EI). Az RST 5,5 szubrutinban dekrementálás és SOD állítása történik ORG 0H ; JMP INIC ;----------------------------------------------------------------------------------------;----------------------------------------------------------------------------------------ORG 28H ; RUTIN: DCR D JNZ TORL ;UGRIK, HA NEM A256. IMP MVI A,0C0H ;SOD=1 PARANCS SZO SIM RET TORL: MVI A,40H ;SOD=0 PARANCS SZO SIM RET ;----------------------------------------------------------------------------------------;----------------------------------------------------------------------------------------ORG 8000H ; INIC: RIM ANI 80H MOV B,A ;ELOZO SID BEALLITASA A B-BE MVI A,4EH ;FELES IT-K MASZKOLASA(KIVETEL RST5.5), SOD=0 SIM XRA A MOV L,A ;L=0

;---------------------------------------------------------------------------------KEZD: RIM ANI 80H MOV D,A ;D=AKTUALIS SID XRA B ;VOLT SID VALTOZAS ? JZ KEZD ;UGRIK, HA NEM VOLT XRA A ORA B ;ELOZO SID „0” VOLT ? JNZ LEFUT ;UGRIK, HA LEFUTO EL FELFUT: EI NOP DI ;------------------------------------------------------------------------------------LEFUT: MOV B,D ;ELOZO ERTEK FRISSITESE JMP KEZD ;----------------------------------------------------------------------------------------;----------------------------------------------------------------------------------------END Digitális technika gyakorlat, 2.félév (9hét) 1 9. „Feles” megszakítások alkalmazása Példa 9.1: Készítsen megszakítási vonalakat kezelő áramkört, amely egy 8085-ös processzoron alapuló sín RST 5.5-ös megszakítási vonalára csatlakozva 3 db külsô megszakítás fogadására alkalmas Egy megszakítási impulzusra csak egyszer kérjen megszakítást. Feltételezzük, hogy a megszakítási

impulzusok gyakorisága max 1ms. A megszakítások kezelését külön-külön áramkörök végzik, amelyek alaphelyzetbe állíthatók a 78H, 79H és 7AH címre adott írás paranccsal. A megszakításkérés lekérdezhető a fenti címekre adott olvasás paranccsal Az RST 5.5-ös megszakítási szubrutinban az IRT1 a „C”, az IRT2 a „D” és az IRT3 az „E” regisztereket inkrementálja. Megoldás 9.1: Javasolt blokkvázlat: Adatsín i8085 Címsin TT WR RD IO/M READY RST 5.5 K K D * T Reset out FF FF * T FF I/O áramkör I/O áramkör ITR1 D * T I/O áramkör K D ITR2 ITR3 9.1 ábra I/O áramkör D0 SN74126 RST 5.5 RD Q WR CLR A4 SN7474 PR CLK D A0 A A1 A2 B IRT1 IRT2 IRT3 C A3 A5 A6 A7 IO/M E1 E2 E3 i8205 Reset out Ready IRTi ( i = 1,2,3 ) 9.2 ábra ; FOPROGRAM RAM STACK IRT1KC IRT2KC IRT3KC IRTKC SZAKIT MASZK MSZ75 T75 EQU EQU EQU EQU EQU EQU EQU EQU EQU EQU 8000H 8100H 78H 79H 7AH 7BH 7CH 0000 1110B 0001 1011B 0001 0000B ;

(2. PELDA) ; (3. PELDA) ; RST 6.5, RST 75 MASZK PARANCS ( 12PELDAK) ; RST 5.5, RST 65 MASZK PARANCS (3 PELDA) ; RST 7.5 FF TORLESE (3 PELDA) Digitális technika gyakorlat, 2.félév (9hét) 2 ; 0RG 0 JMP INIC ; ORG JMP 02CH RUTIN ORG LXI SPHL XRA MOV MOV MOV MVI SIM EI JMP 40H H,STACK ; RST 5.5-OS RUTIN HIVASA ; INIC: ; STACK BEALLITASA A C,A D,A E,A A,MASZK ; C,D,E REGISZTEREK TORLESE ; RST 6.5, RST 75 MASZKOLASA HUROK: ; ; RST 5.5 SZUBRUTIN ; RUTIN: PUSH IN ANI JNZ IN ANI JNZ INR OUT POP EI RET RUT1: INR OUT POP EI RET RUT2: INR OUT POP EI RET END HUROK PSW IRT1KC 1 RU1 IRT2KC 1 RU2 E IRT3KC PSW ; IRT1 MEGSZAKITAS ERKEZETT ? ; IRT2 MEGSZAKITAS ERKEZETT? ; ITR3 LEKEZELESE ; ITR3 MEGSZAKITASI FF. TORLESE C IRT1KC PSW ; ITR1 LEKEZELESE ; ITR3 MEGSZAKITASI FF. TORLESE D IRT2KC PSW ; ITR2 LEKEZELESE ; ITR3 MEGSZAKITASI FF. TORLESE Példa 9.2: Készítsék el a Példa1 megoldását úgy, hogy a megszakítási ff-ok értékei egy utasítással legyenek lekérdezhetők

(cím: 7BH). Megoldás 9.2: D2 IRT3 D1 IRT2 D0 IRT1 SN74126 RST 5.5 RD Q WR CLR A4 SN7474 PR CLK D A0 A A1 A2 B IRT1 IRT2 IRT3 C A3 A5 A6 A7 IO/M E1 E2 E3 i8205 Reset out Ready IRTi ( i = 1,2,3 ) 9.3 ábra ; RST 5.5 SZUBRUTIN ; RUTIN: PUSH PUSH IN MOV PSW H IRTKC H,A Digitális technika gyakorlat, 2.félév (9hét) RU3: RU4: VEGE: RUT1: RUT2: ANI JNZ MOV ANI JNZ MOV ANI JZ INR OUT POP POP EI RET INR OUT JMP INR OUT JMP 3 1 RU1 A,H 2 RU2 A,H 4 VEGE E IRT3KC H PSW ; IRT1 ERKEZETT ? C IRT1KC RU3 D IRT2KC RU4 ; ITR1 LEKEZELESE ; ITR3 MEGSZAKITASI FF. TORLESE ; IRT2 ERKEZETT? ; IRT2 ERKEZETT? ; ITR3 LEKEZELESE ; ITR3 FF. TORLESE ; ITR2 LEKEZELESE ; ITR3 MEGSZAKITASI FF. TORLESE Példa 9.3: Készítsék el a Példa2 megoldását RST 75-es megszakítás alkalmazásával Megoldás 9.3: D2 IRT3 D1 IRT2 D0 IRT1 SN74126 RST 7.5 RD Q WR CLR A4 SN7474 PR CLK D A0 A A1 A2 B IRT1 IRT2 IRT3 C A3 A5 A6 A7 IO/M E1 E2 E3 i8205 Reset out

Ready IRTi ( i = 1,2,3 ) 9.4 ábra ; ; FOPROGRAM ; RAM EQU STACK EQU IRT1KC EQU IRT2KC EQU IRT3KC EQU IRTKC EQU SZAKIT EQU MASZK EQU 8000H 8100H 78H 79H 7AH 7BH 7CH 0000 1110B MSZ75 EQU 0001 1011B T75 EQU 0001 0000B ; (2. PELDA) ; (3. PELDA) ; RST 6.5, RST 75 MASZK ; PARANCS( 1.2PELDAK) ; RST 5.5, RST 65 MASZK ; PARANCS(3. PELDA) ; RST 7.5 FF TORLESE ; (3. PELDA) ; 0RG 0 JMP INIC ; ORG JMP 03CH RUTIN ORG LXI SPHL XRA MOV MOV MOV MVI SIM EI 40H H,STACK ; RST 5.5-OS RUTIN HIVASA ; INIC: ; STACK BEALLITASA A C,A D,A E,A A,MSZ75 ; C,D,E REG. TORLESE ; RST 6.5, 55 MASZKOLASA Digitális technika gyakorlat, 2.félév (9hét) HUROK: JMP HUROK ; ; RST 7.5 SZUBRUTIN ; RUTIN: PUSH PSW PUSH H IN IRTKC MOV H,A ANI 1 ; IRT1 ERKEZETT ? JNZ RU1 RU3: MOV A,H ANI 2 ; IRT2 ERKEZETT? JNZ RU2 RU4: MOV A,H ANI 4 ; IRT2 ERKEZETT? JZ VEGE INR E ; ITR3 LEKEZELESE OUT IRT3KC ; ITR3 FF. TORLESE VEGE: POP H POP PSW MVI A,T75 SIM ; RST 7.5 FF TORLESE OUT SZAKIT ; RST 7.5 FELFUTOEL GEN EI RET

RUT1: INR C ; ITR1 LEKEZELESE OUT IRT1KC ; ITR3 FF. TORLESE JMP RU3 RUT2: INR D ; ITR2 LEKEZELESE OUT IRT2KC ; ITR3 FF. TORLESE JMP RU4 ;------------------------------------------------------------------------------END 4 Digitális technika gyakorlat, 2. félév(10hét) 1 10. Megszakításkezelők alkalmazása (i8259A) Példa10.1: Készítsen áramkört, amely egy 8085-ös processzoron alapuló sínre csatlakozva 8 db külső megszakítás fogadására alkalmas. A. A processzor modul nem tartalmaz megszakítás vezérlőt, a processzor INT és INTA jelei ki vannak vezetve a buszra. A rendszerben egyéb IT kérő eszköz csak a processzor feles IT vonalait használhatja. B. A processzor modul tartalmaz 1db 8259-es megszakításvezérlőt A 8259-es IT bemenetei (IT0.IT7) valamint kaszkád kimenetei (CAS0CAS2) megtalálhatók a buszon A kártya az IT2 vezetékre csatlakozhat. Készítsük el az IT vezérlőket inicializáló rutinokat! a. Báziscím: 20H, IT tábla cím 1C0H,

intervallum: 4 byte b. Processzor moduli vezérlő: Bázis cím: 80h, IT tábla cím 180H, intervallum: 4 byte I. HARDVER MEGVALÓSÍTÁS A. KÜLSŐ IT VEZÉRLŐVEL A0 RD WR INT INTA IO/M DB7.0 RDY* A7.1 G VEZ DIR A0 RD WR INT INTA CS 8259 IR7 D7.0 CAS0 CAS1 CAS2 SP/EN IR0 . IR0 . IR7: Szint vagy él+szint érzékeny, de mindkét esetben a kiszolgálás pillanatában IRi = 1 kell legyen. Digitális technika gyakorlat, 2. félév(10hét) 2 1. VEZ feladata: ### -CS előállítása - a 8259-es mint periféria szerepel CS = sajá tcím ⋅ IO / M ### Adaterősítő vezérlése - INTA alatt - pogramozás alatt (8259 mint periféria) G = CS + INTA (G = CS ⋅ INTA) DIR = IORD + INTA ( DIR = IORD ⋅ INTA) ### RDY* előállítása - INTA alatt - pogramozás alatt (8259 mint periféria) RDY = CS + INTA (Figyelem! INTA alatt IO / M = 1 , más IO eszköz is adhat READY-t) A1 A2 A3 A B C CS 74LS138 A5 E1 A A4 6 A7 IO/M RDY * 0 G E2 E3 7 * INTA DIR RD 2. IT RUTIN

Feladatok: ### Regiszter mentés ### IT kiszolgálás ( IT "törlés" ) ### Regiszter visszaállítás ### IT engedélyezés • 8259 • Processzor a.) Automatikus EOI A következő IT engedélyezése a processzor EI utasításával Használható, ha ### Az IT rutinok nem megszakíthatók ITRUT0: PUSH PSW . . POP PSW EI Digitális technika gyakorlat, 2. félév(10hét) ### Nincs nagy prioritású IT b.) Programozott EOI IT engedélyezése programból Használható, ha ### Az IT rutinok "hosszúak" ### Van nagy prioritású IT Regiszter mentés "Nem megszakítható" műveletek EI További műveletek (IT kiszolgálás) Regiszter visszaállítás 8259 EOI (OCW2) ITRUTi: 3 RET PUSH PSW . ;eddig nem megszakítható . EI ;innen kezdve a magasabb . ;prioritású érvényre juthat . MVI A,20h OUT X59 POP PSW RET B. SLAVE IT VEZÉRLŐVEL Különbségek: ### CAS0.2 vonal kell ### Bufferelt üzemmód: INTA helyett SP / EN Programozás ICW1-ben SNGL = 0

ICW3-ban MASTER: SLAVE: ICW4-ben MASTER: SLAVE: ICW3 i.slave = 1 i M/S = 1 M/S = 0 IT rutinban:EOI a MASTER-re és a SLAVE-re is! (Speciális rögzített prioritású működés!!!) II. PROGRAMOZÁS 8259 felprogramozás (inicilaizálás, maszk állítás), IT tábla kitöltés ICW1: ### Trigger mód állítás ### Tábla cím intervallum ### Master/slave konfiguráció ### ICW4 szükséges? ### IT tábla - alsó byte felső 3 címbit ICW2: ### IT tábla - felső byte 8 címbit (ICW3: ### Master/slave konfigurálás) ICW4: ### ###P típus ### Automatikus EOI ### Master/slave ### Buffrelt üzemmód Digitális technika gyakorlat, 2. félév(10hét) 4 ### spec. rögzített prioritás ICW1, ICW2, ICW4: IT tábla báziscím 01C0H 1 1 0 1 0 1 1 1 ICW1: 0D7h ICW4 lesz Egyedüli vezérlô Cím intervallum: 4 Él + szint C0 0 0 0 0 0 0 0 1 ICW2: 001h 0 0 0 0 0 0 1 0 ICW4: 002h 8085 processzor Automatikus EOI Nem bufferlt üzemmód x Nem SFNM Maszk állítás:

Inicilaizálás után: mindenki engedélyezve - ha tiltani kell, Mi=1-re tiltás ITMASK ICW1 ICW2 ICW4 X59 ITBASE EQU EQU EQU EQU EQU EQU 0FFh 0D7h 001h 002h 020h 001C0H ITINIT: DI MVI OUT MVI OUT MVI OUT MVI OUT LXI MVI MOV INX LXI A,ICW1 X59 A,ICW2 X59+1 A,ICW4 X59+1 A,ITMASK X59+1 H,ITBASE A,0C3h M,A H D,ITRUT0 MOV INX MOV INX INX MOV INX LXI M,E H M,D H H M,A H D,ITRUT1 ; 8259 IO báziscím ; IT tábla báziscím ; Inicializálás alatt IT tiltás ; 8259 inicializálás ; IT maszk állítás ; JMP kódja ; IT0 szubrutin címe ; 4. byte átugrása ; JMP kódja ; IT1 szubrutin címe Digitális technika gyakorlat, 2. félév(10hét) . EI RET ; Inicializálás vége, IT engedélyezés 5 Digitális technika gyakorlat, 2. félév (11hét) 1 Pult illesztése 8085 processzoros rendszerekhez A feladat célja A rendszerbuszon bonyolódó adatforgalom ellenőrzése, a hardware és software belövésének támogatása. A feladat megfogalmazása Tervezzen egy olyan kijelző

és beavatkozó egységet, amely alkalmas egy 8085 bázisú rendszer buszára illesztve az alábbi funkciók megvalósítására: • adat, cím és vezérlőjelek pillanatértékének kijelzésére (adatok és címek hexadecimálisan, vezérlőjelek egyenként); • alkalmas a processzor működésének • gépi ciklusonként • utasítás ciklusonként • valamely cím kialakulásakori választható felfüggesztésére; • lehetővé teszi a program végrehajtásának • gépi ciklusonkénti • utasítás ciklusonkénti léptetését. Megoldás A feladat megoldásához azt használjuk fel, hogy a 8085 processzor gépi ciklusa Tw állapotok beiktatásával tetszés szerinti mértékben megnyújtható ⇒ csak aszinkron buszrendszer esetén működik. Koncepció: a MASTER-SLAVE kapcsolatot ütemező READY jel SLAVE(ek) általi generálását a tervezendő egység felülbírálja. Kihasználjuk továbbá, hogy a FETCH ciklust (utasításkód olvasás) a processzor a státuszbiten

a többi ciklustól megkülönbözteti. 1. részfeladat Hexadecimális kijelző megvalósítása szegmens 1 + 4-ből 7-re dekódolás: kombinációs hálózat, PROM integrált kijelzők Dekóder + szegmens 7 - szinkron - aszinkron (input latch hiánya) Digitális technika gyakorlat, 2. félév (11hét) 2 2. részfeladat Címegyezőség vizsgálat Komparátor áramkörök > ≥ = ≤ < relációkra A0 A3 A>B A>B A=B A<B A=B következő fokozathoz ! A<B B0 B3 INPUT OUTPUT Kaszkádosítás: egyenlő akkor, ha minden digit egyenlő! Teljes egyenlőség: a lánc végén egy db. jel 3. részfeladat 16 bites (nem multiplexelt) címbusz előállítása AD0 A0 D0 Q0 LS 374 AD7 A7 D7 Q7 ALE Többnyire a CPU mellett megvalósított, így a busz nem multiplexelt! (Opcionális!) 4. részfeladat A 16 bites címbusz vagy a címegyezőséghez beállított cím kijelzése CÍMBUSZ (BELSŐ) A>B A=B A<B STOP ON ADDRESS engedélyezve A=B 16 bites

komparátor 16 kapcsoló 16 bites multiplexer beállított cím vizsgálata (célszerűen nyomógomb) 4 digites kijelző Digitális technika gyakorlat, 2. félév (11hét) 3 5. részfeladat Gépi ciklus azonosítás Csak a Fetch kikódolása a cél T1 IO/M 0 0 1 1 0 1 * * * S1 0 1 0 1 1 1 0 X X S0 1 0 1 0 1 1 0 X X Mem Wr Mem Rd I/O Wr I/O Rd Fetch Int Ack HALT HOLD RESET T2 + STOP ON FETCH IO/M ALE S1 S0 D STATUS Q FETCH 74 ALE I/O M C Clear + Megjegyzés: Tápfeszültség bekapcsolásakor nem biztos, hogy korrekt, de ennek nincs jelentősége, mert az első utasítás biztos, hogy FETCH! 6. részfeladat Ready jel generálásának feltétele a) a buszon sínezett Ready jel felszakítandó, ha a megállási feltételek teljesülnek; b) a továbbléptetést kézzel adott impulzus biztosítja. A szöveges feltételekből megállási feltételek STOP ON ADDRESS STA (megállás címegyezőség esetén) STOP ON FETCH STF (megállás utasítás ciklusonként) STOP ON

MACHINE CYCLE STM (megállás gépi ciklusonként) Bemenő jelek: A=B címegyezőség FETCH (Az aktuális gépi ciklus az utasítás első ciklusa) Igazságtábla (eldöntendő a prioritás); megállítandó, ha STM 1 STF X STA X Fetch X 1 0 A=B Megállás X 1 X 1 0 1 X X 0 1 1 0 0 1 X 0 0 0 0 0 X X 0 (Más prioritás is kijelölhető, a feladat szövegéből nem következik.) Digitális technika gyakorlat, 2. félév (11hét) 4 + STF ON Fetch + STM Megállás + A=B STA ON 7. részfeladat Ready kezelés READY SLAVE READY Megállás D ALE 100 n Q READY INT Clock Clear STEP MS 200 s T1 ALE Ready INT Csak akkor lép tovább, ha STEP READY SLAVE van. T2 Digitális technika gyakorlat, 2. félév(13hét) 1 13. Kiemeneti periféria illesztés Feladat: illesztési felület (interface) és működtető program (handler) kialakítása nyomtatóhoz (perifériához). Megvalósítás: szabványos (egységes) interface és protokoll alkalmazása Példa: BSI interfész

és protokoll Az interfész jelei: Jel SO SC AO AC D0.D7 DP Function source operation soure control acceptor operation acceptor operation data lines parity Funkció forrás üzemképes forrás vezérlés nyelő üzemképes nyelő vezérlés adatvonalak paritásbit Protokoll: SO csak ekkor értelmezhetők a további jelek AO SC AC D0-D7 D0-D7 stabil Ez egy un. handshaking (kézfogásos) protokoll, melynek lényege a vezérlőjelek kezdeményezésvisszajelzés párbeszéde Digitális technika gyakorlat, 2. félév(13hét) 8255A 1. üzemmódjában a kimenet -WR D0-D7 max 350 ns -OBF -INTR -ACK min 300 ns max 650 ns max 350 ns Periféria: SC AC Figyelem! új adatot csak itt lehet kivinni Irás (-WR) IT-re, vagy programozott státuszellenőrzés után A port 1. üzemmód kimenetek: -OBF -ACK INTRa PC7 PC6 PC3 2 Digitális technika gyakorlat, 2. félév(13hét) 3 +5V 245 DB0 DB7 -G D0 PA0 D7 PA7 DATA0 DATA7 DIR -G1 -G2 -WR -WR -OBF -RD IO/-M -AEN -INTA

-RDY 244 READY + adatbusz PC7 ∆t SC 360 ns 8255A 7414 -ACK PC6 AC vezérlés PC0 AO -CS AB2 +5V Cím AB7 dekóder -AEN PC1 ERROR PC4 SO INTRa PC3 AB0 AB1 A0 A1 RES 7406 (OC) INT0 INT1 . INT7 CS= saját cím ∗ IO/-M∗-AEN -INTA∗CS=ready, hogy IT alatt ne adjon hamis READY-t G=CS∗(RD+WR) RES Vonal lezárás Digitális technika gyakorlat, 2. félév(13hét) 4 Adatbusz meghajtó: A1 A2 A3 A4 A5 A6 A7 A8 -G B1 B2 B3 B4 B5 B6 B7 B8 DIR G H L L DIR X L H FUNKCIÓ TS BA AB Adatbusz + vezérlő logika: A B C AB2 AB3 AB4 AB5 7400 7486 -E1 -E2 E3 -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 -Y7 -CS55 7404 74LS138 AB6 AB7 -AEN=H: processzor -AEN=L: DMA +5V IO/-M -AEN -INTA -RDY 7406 (OC) -RD -WR -G245 -DIR245 Digitális technika gyakorlat, 2. félév(13hét) IO/-M IO/-MAEN AEN -OBF SC ∆t ∆t biztosítja hogy DATA0.DATA7 előbb legyen stabil, mint SC 01 8255 -OBF↓ max 650 ns minimális időről nem ad tájékoztatást -WR -OBF max 650 ns max 350

ns DATA -OBF max 350 ns SC -ACK max 350 ns min 300 ns 5 Digitális technika gyakorlat, 2. félév(13hét) 6 A ∆t időzítés előállítása egy 74123 típusú monostabil multivibrátorral (Mono Flop) történik. Az időzítés nagyságát az R és C külső passzív elemekkel állíthatjuk be. Értéket az elemknek diagrammból, vagy az alábbi képlet alapján választhatunk. t = k ⋅ R ⋅ C(1 + 0.7 ) R Ahol k=0.28 R C Q -A B -CLR +5V Q A B CLR ↓ H H L H ↑ L H ↑ x x L H x H CK -Q -Q t 1/2 74123 Q -Q L Q0 H -Q0 +5V -OBF B D 74123 RES A működés idődiagramja: -OBF SC B -Q QD -Q CK SC Q 7474 A -CL -CL -PR Digitális technika gyakorlat, 2. félév(13hét) 7 Szoftver: INIT (felprogramozás) Lépések: . 8255 konfigurálás, munkarekeszek alaphelyzetbe állítása . az IT rutin címét az táblába beilleszteni Munka regiszter és jelzők: KH: D7 K D0 H Munka: kiviendő karakter Státusz: státusz Kiviteli rutin: IT rutin: i

INTE8255:=0 HIBA? n k:=1 n k=1 i adat8255:=(munka) munka:=[c] vége k:=0 INTE 8255:=1 vége Digitális technika gyakorlat, 2. félév(13hét) 8 A 8255A programozása: a) Regiszterek Regiszter A port B port C port alsó C port felső Control regiszter Funkció 0,1,2 üzem. ki/be 0,1 üzem. ki/be 0 ,vezérlőjel A porthoz 0 ,vezérlőjel B porthoz üzemmód állítás, Cport bit set/reset Cím: A0,A1 0,0 1,0 0,1 0,1 1,1 Típus RW RW RW RW W CW(kontroll regiszter): D7 1 D6 0 D5 1 D4 0 D3 0 A port 00: 0.üm 01: 1.üm 1x: 2.üm D2 0 C felső 1=be 0=ki A port 1=be 0=ki D1 1 D0 1 B port 1=1 üm 0=0.üm B port 1=be 0=ki D1 b0 D0 1 C alsó 1=be 0=ki üzemmód CW=A3h D7 0 D6 x D5 x D4 x D3 b2 D2 b1 bit s/r 1=set 0=reset bit kiválasztás PC4 set: reset set reset PC6 09h 08h 0Dh 0Ch C port (státusz): D7 IO -OBFa -OBFa D6 IO INTEa INTE1 D5 IBFa IO IBF D4 INTEa IO INTE2 D3 INTRa INTRa INTRa D2 INTEb INTEb B D1 IBFb -OBFb B D0 INTRb INTRb B

irány/üm be/1 ki/1 /2 Digitális technika gyakorlat, 2. félév(13hét) A program: ; ; GLOBAL CONSTANTS X55 EQU 0A0H ;PORT BASE ADDRESS X55 A EQU X55 ;PORT A X55 B EQU X55+1 ;PORT B X55 C EQU X55+2 ;PORT C X55 CT EQU X55+3 ;CONTROL CW55 EQU 0A3H ;ONTROL WORD DISINT EQU 00CH ;DISABLE 8255 IT ENINT EQU 00DH ;ENABLE 825 IT ; ENSO EQU 008H ;ENABLE SO-RESET PC4 DISSO EQU 009H ;DISABLE SO- SET PC4 ; KMASK EQU 080H HMASK EQU 001H PRERR EQU 003H ;PRINTER ERROR IT1MSK EQU 0FDH ;IT ENABLE (8259) EOI EQU 020H ;END OF INTERRUPT(8259) ; PUBLIC X55,CW55,DISINT,ENINT,DISSO,ENSO PUBLIC KMASK,HMASK,PRERR,IT1MSK ; ;* ; DATA SEGMENT ;* ; DSEG PAGE PUBLIC KH,MUNKA,HIBA ; KH: DS 1 MUNKA: DS 1 HIBA: DS 1 ;* ; PRINTER IT ;* ADDRESS ; PRIT: CSEG PUBLIC EXTERN PAGE PRINIT ITTAB,X59 PUSH MVI OUT LDA OUT MVI STA MVI OUT POP EI RET PSW A,DISINT X55 CT MUNKA X55 A A,KMASK KH A,EOI X59 PSW ;IT TABLE, 8259 BASE ;SAVE REGISTER & FLAG ;DISABLE IT 8255 ;OUTPUT CHARACTER TO A ;K:=1 ;ENABLE NEXT IT

(8259) 9 Digitális technika gyakorlat, 2. félév(13hét) ;* ; PRINTER INIT ;* PRINIT: MVI A,CW55 OUT X55 CT MVI A,DISINT OUT X55 CT MVI A,ENSO OUT X55 CT MVI A,KMASK STA KH ; ; STORE IT TO ITTABLE ; MVI A,0C3H ;JMP CODE STA ITTAB+4 ;IT 1 POSITION LXI H,PRIT SHLD ITTAB+5 ; IN X59+1 ;ENABLE IT (8259) ANI ITMSK OUT X59+1 ; RET END ;* ; CHARACTER OUT TO PRINTER ; ; IN: C = CHARACTER TO PRINT ; OUT: CY = 0 - OK ; CY = 1 - ERROR , A = ERROR CODE ; DEST: A,F ;* ; CSEG PAGE PUBLIC PRO EXTERN X55,KMASK,HMASK, PRERR EXTERN KH, MUNKA, HIBA ; PRO: IN X55 C ANI PRERR JNZ P1 ;ERROR IN PRINTER LDA KH ANI KMASK JZ PRO ;WAIT MOV A,C ;PRINT STA MUNKA ;NEXT CHAR XRA A STA KH ; K:=0 MVI A,ENINT OUT X55 CT ;ENABLE IT (8255) RET ; P1: STA HIBA ;ERROR IN PRINTER MVI A,HMASK STA KH LDA HIBA STC RET ; END 10 7 INTEL 8085 gépi utasításkészlete ADATMOZGATÓ UTASÍTÁSOK MOV r1,r2 (r1) <= (r2) Az r2 regiszter tartalmát átírja az r1 regiszterbe. 1 byte: 01DD DSSS 1 gépi ciklus, 4 fázis,

flag-eket nem állítja. MOV r,M (r) <= ((H)(L)) Az r regiszterbe átírja a HL tartalmával kijelölt memóriarekesz tartalmát. 1 byte: 01DD D110 2 gépi ciklus, 7 fázis, flag-eket nem állítja. MOV M,r ((H)(L)) <= (r) A HL tartalmával kijelölt memóriarekeszbe átírja az r regiszter tartalmát. 1 byte: 0111 0SSS 2 gépi ciklus, 7 fázis, flag-eket nem állítja. MVI r,data (r) <= data Az r regiszterbe beírja az utasítás 2. byte-jában megadott adatot 1. byte: 00DD D110 2. byte: data 2 gépi ciklus, 7 fázis, flag-eket nem állítja. MVI M,data ((H)(L)) <= data A HL tartalmával kijelölt memóriarekeszbe beírja az utasítás 2. byte-jában megadott adatot. 1. byte: 0011 0110 2. byte: data 3 gépi ciklus, 10 fázis, flag-eket nem állítja. LXI rp, data16 (rh) <= 3.byte, (rl) <= 2byte A kijelölt rp regiszterpárba beírja az utasítás 2. és 3 byte-jában megadott adatot (data16). 1. byte: 00RP 0001 2. byte: adat (data16) felsô byte 3. byte: adat

(data16) alsó byte 3 gépi ciklus, 10 fázis, flag-eket nem állítja. LDA addr (ACC) <= ((3.byte)(2byte)) Az utasítás 3. és 2 byte-jában megadott címû memóriarekesz (addr) tartalmát beírja az ACC-be. 1. byte: 0011 1010 2. byte: cím (addr) alsó byte 3. byte: cím (addr) felsô byte 4 gépi ciklus, 13 fázis, flag-eket nem állítja. STA addr ((3.byte)(2byte)) <= (ACC) Az ACC tartalmát beírja az utasítás 3. és 2 byte-jában megadott címû (addr) memóriarekeszbe. 1. byte: 0011 0010 2. byte: cím (addr) alsó byte 3. byte: cím (addr) felsô byte 4 gépi ciklus, 13 fázis, flag-eket nem állítja. LHLD addr (L) <= ((3.byte)(2byte)) (H) <= ((3.byte)(2byte)+1) Az utasításban megadott címû (addr) memóriaszó, vagyis két byte tartalmát átmásolja a HL regiszterpárba. 1. byte: 0010 1010 2. byte: cím (addr) alsó byte 3. byte: cím (addr) felsô byte 5 gépi ciklus, 16 fázis, flag-eket nem állítja. SHLD addr ((3.byte)(2byte)) <= (L)

((3.byte)(2byte)+1) <= (H) A HL regiszterpár tartalmát átmásolja az utasításban megadott címû (addr) memóriaszóba, vagyis 2 memóriabyte-ba. !. byte: 0010 0010 2. byte: cím (addr) alsó byte 3. byte: cím (addr) felsô byte 5 gépi ciklus, 16 fázis, flag-eket nem állítja. LDAX rp (A) <= ((rp)) Az rp regiszterpár tartalmával megcímzett memóriabyte-ot átmásolja az ACC-be. Cak a BC és a DE regiszterpár jelölhetô ki. 1. byte: 00RP 1010 2 gépi ciklus, 7 fázis, flag-eket nem állítja. STAX rp ((rp)) <= (ACC) Az rp regiszterpár tartalmával megcímzett memóriabyte-ba másol-ja az ACC-t. Csak a BC és DE regiszterpár jelölhetô ki 1. byte: 00RP 0010 2 gépi ciklus, 7 fázis, flag-eket nem állítja. 7 XCHG (H) <=> (D), (L) <= > (E) Megcseréli a HL és a DE regiszterpárok tartalmát. 1. byte: 1110 1011 1 gépi ciklus, 4 fázis, flag-eket nem állítja. ARITMETIKAI UTASÍTÁSOK ADD r (A) <= (A) + (r) Az ACC-be írja az ACC és az r

regiszter tartalmának összegét. 1. byte: 1000 0SSS 1 gépi ciklus, 4 fázis, állítja a Z,S,P,CY,AC -t. ADD M (A) <= (A) + ((H)(L)) Az ACC-be írja az ACC és a HL által kijelölt memóriabyte tartal-mának összegét. 1. byte: 1000 0110 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC -t. ADI data (A) <= (A) + data Az ACC-be írja az ACC tartalmának és az utasítás 2. byte-jának (data) összegét. 1. byte: 1100 0110 2. byte: data 2 ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t. ADC r (A) <= (A) + (r) + CY Az ACC-be írja az ACC és az r regiszter tartalmának és CY flag összegét. 1. byte: 1000 1SSS 1 ciklus, 4 fázis, állítja a Z,S,P,CY,AC-t. ADC M (A) <= (A) + ((H)(L)) + CY Az ACC-be írja az ACC és a HL regiszterpár tartalmával kijelölt memóriabyte és a CY összegét. 1. byte: 1000 1110 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t. ACI data (A) <= (A) + data + CY Az ACC-be írja az ACC tartalmának, az utasítás 2. bytejának (data), és a

CY összegét. 1. byte: 1100 1110 2. byte: data 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t SUB r (A) <= (A) - (r) Az ACC-be írja az ACC és a kijelölt r regiszter tartalmának különbségét. 1. byte: 1001 0SSS 1 gépi ciklus, 4 fázis, állítja a Z,S,P,CY,AC-t. SUB M (A) <= (A) - ((H)(L)) Kivonja az ACC tartalmából a HL regiszterpár tartalmával kijelölt memóriabyte tartalmát, a különbségét az ACC-ba írja. 1. byte: 1001 0110 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t. SUI data (A) <= (A) - data Az ACC-ba írja az ACC tartalmának és az utasítás 2. byte-jának (data) különbségét. 1. byte: 1101 0110 2. byte: data 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t SBB r (A) <= (A) - (r) - CY Az ACC tartalmából kivonja a r regiszter tartalmát és CY-t, a különbséget az ACC-ba írja. 1. byte: 1001 1SSS 1 gépi ciklus, 4 fázis, állítja a Z,S,P,CY,AC-t. SBB M (A) <= (A) - ((H)(L)) - CY Az ACC tartalmából kivonja a HL

regiszterpár tartalmával kijelölt memórabyte-ot és a CY-t, a különbséget az ACC-ba írja. 1. byte: 1001 1110 2 gépi ciklus, 7 fázis, állitja a Z,S,P,CY,AC-t. SBI data (A) <= (A) - data -CY Az ACC tartalmából kivonja az utasítás 2. byte-ját (data) és a CY-t, a különbséget az ACC-ba írja. 1.byte: 1101 1110 2.byte: data 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t. INR r (r) <= (r) + 1 Eggyel megnöveli a r regiszter tartalmát. Cak a CY flag nem változik meg. 1. byte: 00DD D100 1 gépi ciklus, 4 fázis, állítja a Z,S,P,AC-t. 7 1 gépi ciklus, 4 fázis, flag-eket nem állítja. LOGIKAI UTASÍTÁSOK INR M ((H)(L)) <= ((H)(L)) + 1 Eggyel megnöveli a HL regiszterpár tartalmával kijelölt memóriarekesz tartalmát. Csak a CY flag nem változik meg 1. byte: 0011 0100 3 gépi ciklus, 10 fázis, állítja a Z,S,P,AC-t. ANA r (A) <= (A) ÉS (r) Az ACC és az r regiszter tartalmának logikai ÉS kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és

AC=1 1. byte: 1010 0SSS 1 gépi ciklus, 4 fázis, állítja a Z,S,P,CY,AC-t. DCR r (r) <= (r) - 1 Eggyel csökkenti az r regiszter tartalmát. Cak a CY flag nem változik meg. 1. byte: 00DD D101 1 gépi ciklus, 4 fázis, állítja a Z,S,P,AC-t. ANA M (A) <= (A) ÉS ((H)(L)) Az ACC és a HL tartalmával kijelölt memóriabyte logikai ÉS kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és AC=1 1. byte: 1010 0110 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t DCR M ((H)(L)) <= ((H)(L)) - 1 Eggyel csökkenti a HL regiszterpár tartalmával kijelölt memóriabyte tartalmát. Cak a CY flag nem változik meg 1. byte: 0011 0101 3 gépi ciklus, 10 fázis, állítja a Z,S,P,AC-t. ANI data (A) <= (A) ÉS data Az ACC tartalmának és az utasítás 2. byte-jának (data) logikai ÉS kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és AC=1 1. byte: 1110 0110 2. byte: data 2 gépi ciklus, 7 fázis, állítja Z,S,P,CY,AC-t. INX rp ((rh)(rl)) <= ((rh)(rl)) - 1 A rp

regiszterpár tartalmát eggyel nóveli. Flag-eket nem állítja 1. byte: 00RP 1011 1 gépi ciklus, 6 fázis, flag-eket nem állítja. DCX rp ((rh)(rl)) <= ((rh)(rl)) - 1 Eggyel csökkenti a rp regiszterpár tartalmát.Flag-eket nem állítja. 1.byte: 00RP 1011 1 gépi ciklus, 6 fázis, flag-eket nem állítja. DAD rp (H)(L) <= (H)(L) + (rh)(rl) A HL regiszterpár tartalmához hozzáaadja a kijelölt rp regiszterpár tartalmát, és az eredményt a HL-be írja vissza.Csak a CY flag változik, a legfelsô helyértékrôl származó átviteltôl függôen. 1. byte: 00RP 1001 3 gépi ciklus, 10 fázis, állítja a CY flag-et. DAA (A) bcd <= (A) bin A BCD számok bináris összeadásából származó ACC tartalmat átalakítja BCD kódba (két lépéses 6-korrekció) 1. byte: 0010 0111 XRA r (A) <= (A) KIZÁRÓVAGY (r) Az ACC és az r regiszter tartalmának KIZÁRÓ VAGY kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és A=0 1.byte: 1010 1SSS 1 gépi ciklus, 4 fázis,

állítja Z,S,P,CY,AC-t XRA M (A) <= (A) KIZÁRÓVAGY ((H)(L)) Az ACC és a HL tartalmával kijelölt memóriabyte KIZÁRÓ VAGY kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és AC=0 1.byte: 1010 1110 2 gépi ciklus, 7 fázis, állítja Z,S,P,CY,AC-t. XRI data (A) <= (A) KIZÁRÓVAGY data Az ACC és az utasítás 2. byte-jának KIZÁRÓ VAGY kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és AC=0 1. byte: 1110 1110 2.byte: data 2 gépi ciklus, 7 fázis, állítja Z,S,P,CY,AC-t. ORA r (A) <= (A) VAGY (r) 7 Az ACC és az r regiszter tartalmának VAGY kapcsolatát visszaírja az ACC-ba.Mindig CY=0, és AC=0 1.byte: 1011 0SSS 1 gépi ciklus, 4 fázis, állítja Z,S,P,CY,AC-t. ORA M (A) <= (A) VAGY ((H)(L)) Az ACC és a HL tartalmával kijelölt memóriabyte VAGY kapcsolatát visszírja az ACC-ba. Mindig CY=0, és AC=0 1.byte: 1011 0110 2 gépi ciklus, 7 fázis, állítja Z,S,P,CY,AC-t. ORI data (A) <= (A) VAGY data Az ACC és az utasítás 2. byte-jának (data)

VAGY kapcsolatát visszaírja az ACC-ba. Mindig CY=0, és AC=0 1. byte: 1111 0110 2. byte: data 2 gépi ciklus, 7 fázis, állítja Z,S,P,CY,AC-t. CMP r (A) - (r) Kivonja az ACC-ból az r regiszter tartalmát és a flag-eket állítja. Z=1, ha (A) = (r) és CY=1, ha (A)<(r). 1. byte: 1011 1SSS 1 gépi ciklus, 4 fázis, állítja Z,S,P,CY,AC-t. CMP M (A) - ((H)(L)) Kivonja az ACC-ból a HL tartalmával kijelölt memóriabyte-ot és beállítja a flag-eket.Z=1, ha (A)=((H)(L)) és CY=1, ha (A)<((H)(L)). 1.byte: 1011 1110 2 gépi ciklus, 7 fázis, állítja Z,S,P,CY,AC-t. CPI data (A) - data Kivonja az ACC-ból az utasítás 2. byte-ját (data) és beállítja a flag-eket. Z=1, ha (A)=data és CY=1, ha (A)<data 1.byte: 1111 1110 2.byte: data 2 gépi ciklus, 7 fázis, állítja a Z,S,P,CY,AC-t. RLC (An+1)<=(An), (A0)<=(A7), CY<=(A7) Az ACC tartalmát körbe lépteti balra. A 7 bit átírodik a CY-ba és a 0.bitbe is Csak a CY flag változhat 1. byte: 0000 0111 1 gépi

ciklus, 7 fázis, csak a CY-t állítja. RRC (An)<=(An+1), (A7)<=(A0), CY<=(A0) Az akkumulátor tartalmát körbe lépteti jobbra . A 0 bit beírodik a CY-ba és a 7. bitbe is Csak a CY flag változhat 1. byte: 0000 1111 1 gépi ciklus, 4 fázis, csak a CY-t állítja. RAL (An+1)<=(An), CY<=(A7), (A0)<=CY Az ACC és a CY tartalmát balra lépteti körbe, a CY-on keresztül. A CY a 0 bitbe, a 7bit a CY-ba írodik át Csak CY flag változhat. 1. byte: 0001 0111 1 gépi ciklus, 4 fázis, csak a CY-t állítja. RAR (An)<=(An+1), (A7)<=CY, CY <= (A0) Az ACC és a CY tartalmát jobbra lépteti körbe, a CY-on keresztül.A CY a 7 bitbe, a 0 bit a CY-ba irodik átCsak CY flag változhat. 1. byte: 0001 1111 1 gépi ciklus, 4 fázis, csak a CY-t állítja. CMA (A)<= NOT (A) Az ACC tartalmát bitenként megnegálja. 1. byte: 0010 1111 1 gépi ciklus, 4 fázis, flag-eket nem állítja. CMC CY<= NOT CY A CY flag-et megnegálja. 1. byte: 0011 1111 1 gépi ciklus, 4

fázis, csak CY-t állítja. STC CY <= 1 Logikai 1-be állítja a CY flag-et. 1. byte: 0011 0111 1 gépi ciklus, 4 fázis, csak CY-t állítja. UGRÓ UTASÍTÁSOK Feltételek megadása: mnem. kód NZ Z NC C PO PE P M flag érték Z=0 Z=1 CY=0 CY=1 P=0 P=1 S=0 S=1 opkód CCC 000 001 010 011 100 101 110 111 7 JMP addr (PC) <= ((byte3)(byte2)) Feltétel nélkül az utasításban megadott címen (addr)folytatja a programvégrehajtást. 1. byte: 1100 0011 2. byte: addr alsó byte 3. byte: addr felsô byte 3 gépi ciklus, 10 fázis, flag-eket nem állítja. Jcond addr ha cond=IGAZ, akkor (PC) <= ((byte3)(byte2)) Ha az utasításban megadott feltétel teljesül, akkor az utasításban megadott címen (addr), egyébként a Jcond utáni utasításon folytatja a programvégrehajtást. Az utasítás végrehajtási ideje lerövidül, ha a feltétel nem teljesül. 1. byte: 11CC C010 2. byte: addr alsó byte 3. byte: addr felsô byte 2/3 ciklus, 7/10 fázis, flag-eket nem állítja.

CALL addr ((SP)-1) <= (PCfelsô) ((SP)-2) <= (PCalsó) (SP) <= (SP)-2 (PC) <= ((byte3)(byte2)) Feltétel nélküli szubrutinhívás, amely elöször kimenti a stackbe a CALL utáni utasítás címét majd a szubrutinkezdôcímmel (addr) felülírja a PC-t és kettôvel csökkenti a SP tartalmát. 1. byte: 1100 1101 2. byte: addr alsó byte 3. byte: addr felsô byte 5 gépi ciklus, 18 fázis, flag-eket nem állítja Ccond addr ha cond=IGAZ, akkor ((SP)-1 <= (PCfelsô) ((SP)-2 <= (PCalsó) (SP) <= (SP)-2 (PC) <= ((byte3)(byte2)) Feltételes szubrutínhívás, amelynek eredménye a CALL utasítás eredményével azonos, ha a feltétel teljesül, egyébként a Ccond utáni utasításon folytatódik a programvégrehajtás. A végrehajtási idô lerövidül, ha a feltétel nem teljesül. 1. byte: 11CC C100 2. byte: addr alsó byte 3. byte: addr felsô byte 2/5 ciklus, 9/18 fázis, flag-eket nem állítja. RET (PCalsó) <= ((SP)) (PCfelsô) <= ((SP)+1) (SP) <=

(SP)+2 Feltétel nélküli visszatérés szubrutinból a meghívó CALL tip. uta-sítás utáni utasításra mutató, a stack-be kimentett visszatérési címre. A stack-bôl visszaolvasott cím felülírja a PC-t, a SP kettôvel megnô. 1. byte: 1100 1001 3 gépi ciklus, 10 fázis, flag-eket nem állítja. Rcond ha cond=IGAZ, akkor (PCalsó) <= ((SP)) (PCfelsô) <= ((SP)+1) (SP) <= (SP)+2 Feltételes visszatérés szubrutinból. Ha az utasításban megadott feltétel teljesül akkor a szubrutint meghívó CALL tip. utasítás utáni utasításra mutató, a stack-be kimentett visszatérési címen folytatódik a programvégrehajtás, egyébként az Rcond utáni utasításon. A stack-bôl visszaolvasott cím felülírja a PC-t, a SP kettôvel megnô. A végrehajtási idô függ a feltétel teljesülésétôl. 1. byte: 11CC C000 1/3 gépi ciklus, 6/12 fázis, flag-eket nem állítja. RST n ((SP)-1) <= (PCfelsô) ((SP)-2) <= (PCalsó) (SP) <= (SP)-2 (PC) <= 8*n

(ahol n=0,1,2.,7) Egy byte-os szubrutinhívó utasítás, a szubrutin kezdôcíme az utasításban megadott n ( a mûveleti kód NNN bitjeinek decimális értéke ) szám nyolcszorosa ( decimális 0, 8, .48, 56 mivel n<8 ). 1. byte: 11NN N111 3 gépi ciklus, 12 fázis, flag-eket nem állítja. PCHL (PCfelsô) <= (H) (PCalsó) <= (L) Az utasítás átírja a HL regiszterpár tartalmát a PC-be, így a programvégrehajtás a HL-ben tárolt címen folytatódik. 1. byte: 1110 1001 1 gépi ciklus, 6 fázis, flag-eket nem állítja. Stack, I/O és vezérlô utasítások PUSH rp ((SP)-1 <= (rp felsô) ((SP)-2 <= (rp alsó) (SP) <= (SP)-2 Az kijelölt rp regiszterpár (SP nem lehet !) tartalmát kimenti a stack-be, a SP-t kettôvel csökkenti. 1. byte: 11RP 0101 7 3 gépi ciklus, 12 fázis, flag-eket nem állítja 1 gépi ciklus, 6 fázis, flag-eket nem állítja. IN port (A) <= input port Az ACC-ba írja az utasításban megadott címû bemeneti port-ról beolvasott

byte-ot. 1. byte: 1101 1011 2. byte: port 3 gépi ciklus, 10 fázis, flag-eket nem állítja. PUSH PSW ((SP)-1 <= (A) ((SP)-2 <= (flag byte) (SP) <= (SP)-2 A (SP)-1 címre az ACC tartalmát, a (SP)-2 címre a flagekbôl képzett byte-ot menti ki. A SP-t kettôvel csökkenti Flag byte: D7 D6 D5 D4 D3 D2 D1 D0 S Z X AC X P X CY ahol X=közömbös 1. byte: 1111 0101 3 gépi ciklus, 12 fázis, flag-eket nem állítja. POP rp (rp alsó) <= ((SP)) (rp felsô) <= ((SP)+1) (SP) <= (SP)+2 A SP által kijelölt két memóriabyte tartalmát ( stack-be kimentett érték) átírja a kijelölt rp regiszterpárba. A SP-t kettôvel megnöveli. 1. byte: 11RP 0001 3 gépi ciklus, 10 fázis, flag-eket nem állítja. POP PSW (flag byte) <= ((SP) (A) <= ((SP)+1 A stack-bôl ( amelyet a SP elölt ki) visszaállítja a flag-ek, valamint az ACC tartalmát. A SP-t kettôvel megnöveli 1. byte: 1111 0001 3 gépi ciklus, 10 fázis, állítja Z,S,P,CY,AC-t XTHL (L) <= > ((SP)) (H)

<=> ((SP)+1 Megcseréli a HL regiszterpár és a stack 2 legfelsô byte-jának (SP jelöli ki) tartalmát. A SP nem változik 1. byte: 1110 0011 5 gépi ciklus, 16 fázis, flag-eket nem állítja. SPHL (SP) <= (H)(L) A HL regiszterpár tartalmát közvetlenül átírja a SP-be. 1.byte: 1111 1001 OUT port output port <= (A) Az ACC tartalmát kiviszi az utasításban megadott címû kimeneti portra. 1. byte: 1101 0011 2. byte: port 3 gépi ciklus, 10 fázis, flag-eket nem állítja. EI INTE FF <= 1 A megszakítás elfogadása engedélyezett lesz az EI utáni utasí-tás végrehajtása után. 1.byte: 1111 1011 1 gépi ciklus, 4 fázis, flag-eket nem állítja. DI INTE FF <= 0 A megszakításkérés elfogadása letiltottá válik közvetlenül a DI utasítás végrehajtása után. Az utasítás végrehajtása közben nem figyeli a megszakításkéréseket. 1. byte: 1111 0011 1 gépi ciklus, 4 fázis, flag-eket nem állítja. HLT A CPU HALT állapotba kerül a HLT

végrehajtása közben kiadott 2. ALE impulzus után (2 gépi cklus elején) 1. byte: 0111 0110 1.5 gépi ciklus, 5 állapot, flag-eket nem állítja NOP Üres utasítás bármely adat megváltozása vagy mûvelet nélkül. 1. byte: 0000 0000 1 gépi ciklus, 4 fázis, flag-eket nem állítja. RIM (A) <= megszakítás maszk Az utasítás az ACC-ba olvassa az alábbi információkat: A0: RST5.5 maszkbitje (ha 1, akkor tiltott) A1: RST6.5 maszkbitje (ha 1, akkor tiltott) A2: RST7.5 maszkbitje (ha 1, akkor tiltott) A3: INTE FF (általános megszakít. engedélyezés) A4: megszakításkérés az RST5.5-ön 7 A5: megszakításkérés az RST6.5-ön A6: megszakításkérés az RST7.5-ön A7: SID bemenetrôl (soros adatbemenet) beolvasott érték 1. byte: 0010 0000 1 gépi ciklus, 4 fázis, flag-eket nem állítja. SIM Az utasítás elôtt betöltött ACC tartalom alapján beállítja a megszakítás-maszkokat és a SOD soros adatkimenetet. A3=1 engedélyezi a maszkbeállítást az

A0,A1,A2 biteken A0=1 és A3=1 letiltja az RST5.5 megszakítást, A1=1 és A3=1 letiltja az RST6.5 megszakítást, A2=1 és A3=1 letiltja az RST7.5 megszakítást, A4=1 törli az RST7.5 tároló flip-flopot, A5: közömbös A6=1 engedélyezi a SOD kimenet beállítását, A7 => SOD, ha A7=1. 1. byte: 0011 0000 1 gépi ciklus, 4 fázis, flag-eket nem állítja. JELÖLÉSEK bitek sorszámozása: 7 = byte legfelsô helyértéke 0 = byte legkisebb helyértéke (.) : regiszter, regiszterpár, vagy memória tartalma A, ACC : 8 bites akkumulátor addr : 16 bites memóriacím data : 8 bites adat data16 : 16 bites adat byte2 : utasítás 2. byte-ja byte3 : utasítás 3. byte-ja port : kiviteli vagy beviteli port 8 bites közvetlen címe r, r1, r2 : az A,B,C,D,E,H,L 8 bites regiszter (jelölésük a mnemonikban: A B C D E H L) rp : a BC, DE, HL, SP 16 bites regiszterpár (jelölésük a mnemonikban: B D H SP) DDD,SSS: regiszterkijelölô bitkombináció az utasításkódban 111 => A 000

=> B 001 => C 010 => D 011 => E 100 => H 101 => L RP : regiszterpárt kijelölô bitkombináció az utasításban 00 => BC 01 => DE 10 => HL 11 => SP PC : 16 bites programszámláló SP : 16 bites stack pointer Ai : az akkumulátor i-edik bitje Z,S,P,CY,AC: flag-ek Z => zero flag S => elöjel (sign) flag P => páratlan paritás flag CY => átvitel (carry) flag AC => segédátvitel (auxiliary carry) flag <= , = > : egyirányú adatmozgatás iránya <=> : kétirányú adatcsere NNN : 3bites kombináció, amely 0.7 közötti számot jelöl n : az NNN kombinációval decimális szám 8-9 Mérés Logikai hálózatok tervezése és szimulációja 1. A mérés célja Szöveges feladat alapján logikai hálózat tervezése LOG-IC tervezôrendszer segítségével. A megtervezett hálózat logikai szimulációja. A tervezôrendszer által szolgáltatott eredmények értékelése, az állapotkód és a megvalósító flip-flop

megválasztás hatása a hálózat bonyolultságára. 2. Elméleti alapismeretek - Kombinációs hálózatok tervezése - Sorrendi hálózatok tervezése - Vezérlô egységek tervezése 3. Felkészülés a mérésre 3.1 Az elméleti alapismeretek átismétlése 3.2 A kiadott mérési segédlet tanulmányozása, a LOG/IC tervezôrendszer leíró nyelvének megismerése. 4. A mérés menete 4.1 A mérés elején megkapott szöveges feladat alapján a specifikációnak megfelelô hálózat megadása a tervezôrendszer leíró nyelvén 4.2 A helyes mûködés ellenôrzése a szimulátorral Tipikus bemeneti sorozatok generálása 4.3 Különbözô állapotkód választás esetén a kódválasztás hatásának vizsgálata a hálózat bonyolultságára 4.4 A megvalósító flip-flop megválasztásának hatása a hálózat bonyolultságára 4.5 Jegyzôkönyv készítés A jegyzôkönyvnek tartalmaznia kell - a kiadott feladatot - a tervezôrendszer formális nyelvén leírt megoldást - a

szimuláció eredményeit ( idôdiagramok ) - a tervezôrendszer által szolgáltatott eredményeket és az ebbôl levont következtetéseket 5. Kidolgozott mintafeladat Tervezzünk dobókockát helyettesítô sorrendi hálózatot, melynek a mûködése a következô: A hálózat 3 bemenettel és 7 kimenettel rendelkezik. A start bemenettel "dobhatunk", a mode bemenettel a "dobás" algoritmusát választhatjuk meg, a test bemenet a kijelzôk llenôrzésére szolgál. A d1 d7 kimenetek a dobókocka pontjainak megfelelô elhelyezkedésû LED diódák begyújtását végzik, és negatív logikájúak (A LED ég, ha a kimenet 0 értékû). +-------+ start-| |- d1 | |- d2 mode-| |- d3 | |- d4 test-| |- d5 | |- d6 | |- d7 +-------+ start: mode: test: +--------------------+ |(d1) (d5)| | | |(d2) (d4) (d6)| | | |(d3) (d7)| +--------------------+ 1 - a dobókocka kijelzôje folyamatosan, az órajel ütemében változik 0 - az utolsó érték látszik a kijelzôn 1 -

egyesével felfelé számol 0 - egyesével lefelé számol 1 - az összes led ég ( az összes kimenet 0 ) 0 - normál mûködés 1 5.1 A feladat leírása LOG/IC nyelven A hálózat egy 7 állapottal rendelkezô szinkron sorrendi hálózattal írható le. Az egyes állapotok a következôk: S1 . S6 - A kocka pillanatnyi értékének megfelelô állapotok S7 - Test állapot, az összes kimenet 0 értékû A kimenetek értékei az egyes állapotokban megfelelnek a LED-ek vezérléséhez szükséges kombinációval (MOORE modell ponált logika): állapot S1 S2 S3 S4 S5 S6 S7 d1,d2,d3,d4,d5,d6,d7 0, 0, 0, 1, 0, 0, 0 1, 0, 0, 0, 0, 0, 1 1, 0, 0, 1, 0, 0, 1 1, 0, 1, 0, 1, 0, 1 1, 0, 1, 1, 1, 0, 1 1, 1, 1, 0, 1, 1, 1 1, 1, 1, 1, 1, 1, 1 A bemenetek értékének függvényében a következô állapotátmenetek adódnak: Ha test = 1 Sn -> S7 következô állapot mindíg a test állapt Ha test = 0 és start= 0 Sn -> Sn marad az eredeti állapot Ha test = 0 és start= 1 mode = 0 Sn

-> Sn-1 lefelé számlál mode = 1 Sn -> Sn+1 felfelé számlál Állapotkódnak elsô közelítésben válasszunk binárs kódolást. Mivel összesen 7 állapotunk van, 3 szekunder változó elegendô a megvalósításhoz, és az egyes állapotokhoz a tervezô rendszer automatikusan a következô kódokat fogja rendelni: S1 - 000, S2 - 001, . , S7 - 110. A LOG/IC file: *IDENTIFICATION Dobókocka Állapotkód választás: bináris Flip-flop: D *X-NAMES start, mode, test; bemenetek *Z-NAMES d[1.7]; MOORE kimenetek *LEVEL LOW = d[1.7]; A kimenetek negált logikájúak *Z-VALUES S1 = 0001000; S2 = 1000001; S3 = 1001001; S4 = 1010101; S5 = 1011101; S6 = 1110111; S7 = 1111111; ! A Moore kimenetek értékei ponált logikával megadva ; Az állapottábla *FLOW-TABLE Relevant = test = 1 ; minden LED ég S[1.7],F7 ; RELEVANT = test = 0, start, mode; S[1.7], X0- , F[17] ; marad az elozô állapot S[1.5], X10 , F[26] ; felfelé számlál S6 , X10 , F1 ; S7 , X10 , F1 ; S[2.6], X11 ,

F[15] ; lefelé számlál S1 , X11 , F6 ; S7 , X11 , F6 ; ; Állapotkód választás *STATE-ASSIGNMENT BINARY ; elôször legyen bináris kód ; A megvalositó flip-flop definiálása *FLIPFLOPS D-FF; ; elôször legyen D *RUN-CONTROL LISTING = LONG ; teljes lista *END 2 5.2 Szimuláció A szimuláció során funkcionálisan ellenôrizhetjük a megtervezett hálózatot. Bemeneti jelsorozatként interaktív módon olyan sorozatot választunk, amellyel ellenôrizni tudjuk a "kritikus" állapotátmeneteket. Példánkban elôször a test bemenet hatását ellenôrizzük, majd felfelé számláltatunk, megvárjuk az átfordulást, lefelé számláltatunk, start=1 mellett állitjuk a test bemenetet, végül leállítjuk a számlálást. A tesztelésnél problémát jelent, hogy mi lesz az alapállapot, vagyis "bekapcsolás" után az állapotváltozók flip-flopjai milyen értéket vesznek fel. Ez különösen fontos akkor, ha az összes állapotkódot nem

használtuk fel, a kódolás során közömbös állapotkód kombinációk is maradtak. Ebben az esetben a hálózat bekapcsolása utáni viselkedése véletlenszerû lesz, a szimulátor nem lesz képes a mûködés követésére. Mi ezt a problémát példánkban a szimulátor preload funkcióját kihasználva oldjuk meg úgy, hogy az állaptt flip-flopok kiindulási értékét 0-ra rögzítjük. Valódi PAL eszköz esetén ezt a hatást úgy érhetjük el, hogy olyan típust alkalmazunk, amely flip-flopjai rendelkeznek törlô bemenettel (reset), és a hálózatunkban definiálunk egy alaphelyzetbe állító jelet, amely ezt a bemenetet aktivizálja. A szimuláció eredménye: E S S v t T M T e a A O E Q Q Q n t R D S Q Q Q D D D D D D D t e T E T 3 2 1 1 2 3 4 5 6 7 ----------------------------------------------------------------------------# # 0-1 0-1 0-1 : 0-1 0-1 0-1 0-1 0-1 0-1 0-1 0-1 0-1 0-1 ----------------------------------------------------------------------------1 IP :