A doksi online olvasásához kérlek jelentkezz be!

A doksi online olvasásához kérlek jelentkezz be!

| Anonymus | 2022. január 03. | |

|---|---|---|

| Az alap információk kibontása közepes szintre, siker, mivel e doksinak ez volt a célja. Király, bár van egy két elavult információ benne, érdemes lenne frissíteni. | ||

Mit olvastak a többiek, ha ezzel végeztek?

Tartalmi kivonat

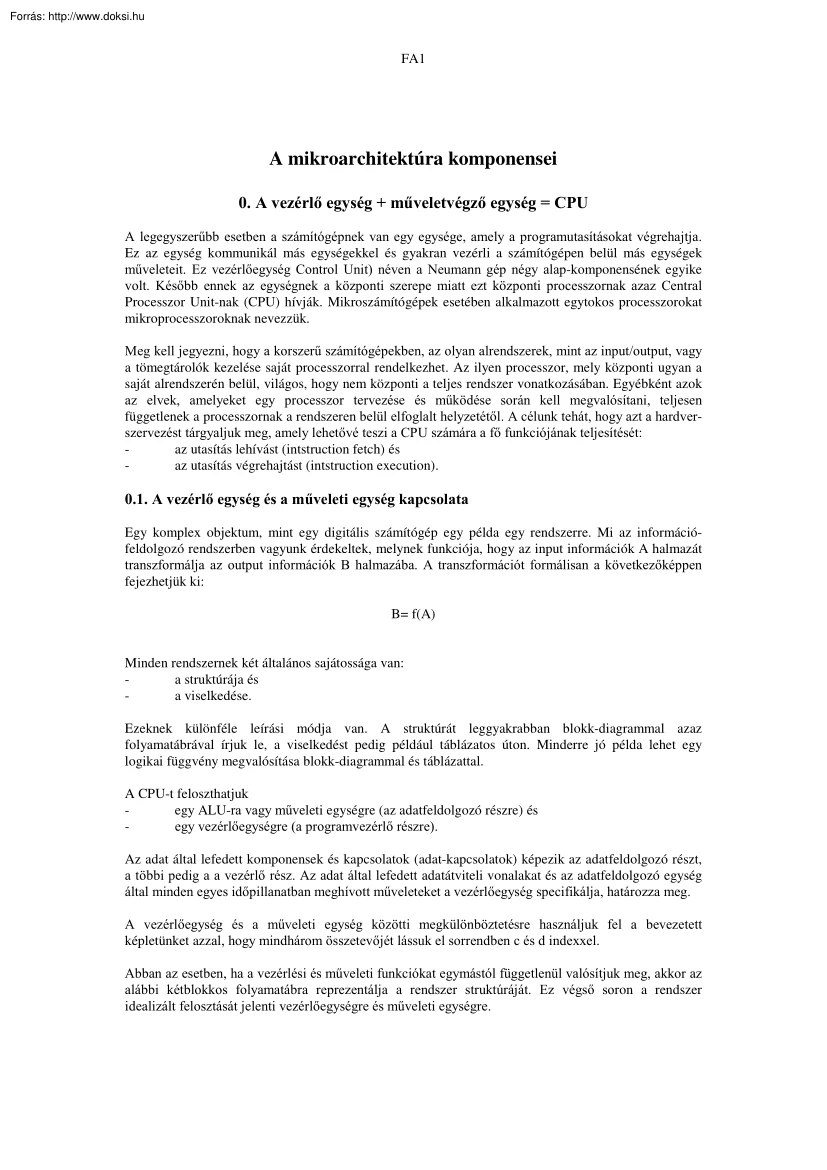

FA1 A mikroarchitektúra komponensei 0. A vezérlő egység + műveletvégző egység = CPU A legegyszerűbb esetben a számítógépnek van egy egysége, amely a programutasításokat végrehajtja. Ez az egység kommunikál más egységekkel és gyakran vezérli a számítógépen belül más egységek műveleteit. Ez vezérlőegység Control Unit) néven a Neumann gép négy alap-komponensének egyike volt. Később ennek az egységnek a központi szerepe miatt ezt központi processzornak azaz Central Processzor Unit-nak (CPU) hívják. Mikroszámítógépek esetében alkalmazott egytokos processzorokat mikroprocesszoroknak nevezzük. Meg kell jegyezni, hogy a korszerű számítógépekben, az olyan alrendszerek, mint az input/output, vagy a tömegtárolók kezelése saját processzorral rendelkezhet. Az ilyen processzor, mely központi ugyan a saját alrendszerén belül, világos, hogy nem központi a teljes rendszer vonatkozásában. Egyébként azok az elvek, amelyeket egy

processzor tervezése és működése során kell megvalósítani, teljesen függetlenek a processzornak a rendszeren belül elfoglalt helyzetétől. A célunk tehát, hogy azt a hardverszervezést tárgyaljuk meg, amely lehetővé teszi a CPU számára a fő funkciójának teljesítését: az utasítás lehívást (intstruction fetch) és az utasítás végrehajtást (intstruction execution). 0.1 A vezérlő egység és a műveleti egység kapcsolata Egy komplex objektum, mint egy digitális számítógép egy példa egy rendszerre. Mi az információfeldolgozó rendszerben vagyunk érdekeltek, melynek funkciója, hogy az input információk A halmazát transzformálja az output információk B halmazába. A transzformációt formálisan a következőképpen fejezhetjük ki: B= f(A) Minden rendszernek két általános sajátossága van: a struktúrája és a viselkedése. Ezeknek különféle leírási módja van. A struktúrát leggyakrabban blokk-diagrammal azaz folyamatábrával

írjuk le, a viselkedést pedig például táblázatos úton. Minderre jó példa lehet egy logikai függvény megvalósítása blokk-diagrammal és táblázattal. A CPU-t feloszthatjuk egy ALU-ra vagy műveleti egységre (az adatfeldolgozó részre) és egy vezérlőegységre (a programvezérlő részre). Az adat által lefedett komponensek és kapcsolatok (adat-kapcsolatok) képezik az adatfeldolgozó részt, a többi pedig a a vezérlő rész. Az adat által lefedett adatátviteli vonalakat és az adatfeldolgozó egység által minden egyes időpillanatban meghívott műveleteket a vezérlőegység specifikálja, határozza meg. A vezérlőegység és a műveleti egység közötti megkülönböztetésre használjuk fel a bevezetett képletünket azzal, hogy mindhárom összetevőjét lássuk el sorrendben c és d indexxel. Abban az esetben, ha a vezérlési és műveleti funkciókat egymástól függetlenül valósítjuk meg, akkor az alábbi kétblokkos folyamatábra reprezentálja

a rendszer struktúráját. Ez végső soron a rendszer idealizált felosztását jelenti vezérlőegységre és műveleti egységre. FA1 A c A d vezérlõegység mûveleti egység B c B d Bc=fc(Ac) Bd=fd(Ad,Ac) Bár egységes jelölés nincs, alapvetően kétféle jelölési módot használnak az adatáramlási és a vezérlőjel-áramlási utak megkülönböztetésére. adat szimpla vonal. vezérlőjel pedig szaggatott; az adat dupla vonal, a vezérlőjel pedig szimpla. A diagramm világosan rámutat a műveleti és a vezérlőegység közötti okozati viszony implicit megkülönböztetésére: az Ac vezérlési input hat a műveleti egység viselkedésére, de az adat input semmiféle hatást nem gyakorol a vezérlőegységre. A gyakorlatban azonban az adatfeldolgozó és a programvezérlő rész közötti elhatárolás nem ennyire egyértelmű, mint azt az eddigiekben mutattuk. Gyakran a folyamatábra adatfeldolgozási részének is megengedett, hogy a vezérlőegységre

hatást gyakoroljon. Például a CPU-n belül végzett aritmetikai művelet túlcsordulást, előjelváltást, nulla kialakulását eredményezheti, s ezt a tényt fel lehet használni a vezérlőegység alternatív módon történő viselkedésére. Ezért fc mind az Ac mind pedig az Ad-től függővé válik: A c Ad vezérlőegység mûveleti egység B c Bd Bc=fc(Ad,Ac) Bd=fd(Ad,Ac) Ez az ábra már végső soron a rendszer szokásos felosztását jelenti vezérlőegységre és műveleti egységre. A két komponens közötti okozati viszony bonyolulttá, nem egyértelművé, sőt szubjektívvé teszi a rendszerek elhatárolását. Ugyanazok a jelek bizonyos esetekben vezérlőjeleknek tekinthetők a tervezés folyamán, máskor pedig adatjeleknek. Feltételezzük, hogy a rendszert blokk-diagramm formájában specifikáltuk. Ha minden blokkot felosztunk vezérlési és adatfeldolgozási részre, akkor az eredő diagrammot tekinthetjük két diagrammot tartalmazónak: az egyik

csak a vezérlőegységet, a másik pedig az adatfeldolgozó részt tartalmazza. Ekkor nem nehéz számunkra vízuálisan megkülönböztetnünk a két különálló, de összekapcsolódó alrendszert: az egyik az adatfeldolgozó, a másik pedig a vezérlőegység. Ez a felosztás azért is fontos, 2 FA1 mivel a vezérlőegységet és az adatfeldolgozó egységet általában különállóan, függetlenül tervezik. Ezen túlmenően a rendszereket megkülönböztetik aszerint is, hogy hogyan valósítják meg a legfontosabb vezérlési funkcióikat. Ha a vezérlőegység logikai áramkörökből áll és így az fc alapvetően állandó, akkor a rendszert huzalozottnak hívják. Ha pedig az fc megvalósítása memóriában tárolt vezérlési információkkal történik, és a vezérlési funkciók inkább szoftver, mint hardver úton valósulnak meg, akkor mikroprogramozott vezérlésről beszélünk. 0.2 Belső sínrendszer A központi egységen belüli belső sínek, melyek

hasonlók a külső sínrendszerhez, itt is információk száguldanak. A sín egy vezeték-köteg, melyen párhuzamosan áramlanak a bitek, továbbá a vezérlő információk. A busz rossz kifejezés, rossz asszociációt ad: a buszon egyszerre sokan utaznak, a sínen egyszerre csak egy bit lehet, tehát inkább egy fekete Mercedes a jó kifejezés. A számítógépekben, hogy megfelelő sebeséggel működjenek, párhuzamos adatáramlást kell biztosítani. Ez azt jelenti, hogy annak érdekében, hogy egy komponens egyidejűleg egy egész adatszót tudjon kezelni, a komponensek közötti adatátvitelnek párhuzamosan kell történnie, azaz egy szó valamennyi bitjét szimultán módon kell átvinni. Ennek érdekében ennek megfelelő számú vezeték (vonal) szükséges a kapcsolatok kialakításához. Ezt a bizonyos közös tulajdonságokkal rendelkező vezetéknyalábot hívják sínnek vagy busznak. A belső sínrendszer esetében a vezérlésre szolgáló vezetékek nem

szerepelnek a sínrendszer részeként, mivel a vezérlés módjából adódóan az nem különül el önálló rendszerként. A számítógépen belül a sínrendszer nem csak a processzor és más, a processzoron kívüli eszközök összekötésére szolgál, hanem magán a processzoron belül is kialakítottak egy belső sínrendszert. Ennek megfelelően megkülönböztetünk: belső sínrendszert és külső sínrendszert. Az utóbbival majd a félév végén fogunk foglalkozni, önálló előadás keretében. A belső sínrendszer kialakítását az elérni kívánt teljesítmény szabja meg. A CPU-n belüli komponensek ugyanis sokféleképpen kapcsolhatók össze. Az egyes komponensek összekapcsolási módja jelentős hatásal van a CPU műveleti sebességére, következésképpen ez az egyik olyan sajátosság, ami megkülönbözteti az egyik CPU-t a másiktól. A CPU-n belüli átviteli sínrendszerek a következőképpen alakíthatók ki: 0.21 Pont-pont vagy dedikált

sínrendszer Egy egyszerű CPU esetében, mely csupán egyetlen felhasználói regisztert ismer, az akkumulátort, összesen tíz sínnel, nevezetesen négy címsínnel és hat - utasítást és operandust továbbító - adatsínnel kell rendelkeznie. Nyilvánvaló, hogy amennyiben több regiszter érhető el számunkra és több utasítást biztosítunk, akkor több sínre van szükségünk. Minden szükséges információ átvitel számára ebben az esetben dedikált sínt biztosítunk. Az ilyen adatátviteli mód előnye, hogy sok adatátvitel történhet párhuzamosan, így ez a tendencia vezet a gyors CPU felé. A hátránya viszont, hogy igen drága lenne valamennyi sín biztosítása Ha tanulmányozzuk egy gépi utasítás műveletéhez szükséges átviteleket, kiderül, hogy az átvitelek többsége logikailag nem történhet párhuzamosan még akkor sem, ha ezt a lehetőséget fizikailag biztosítjuk. Következésképpen a CPU belső sín szervezésénél egy teljesen

dedikált vonalú szervezés gyakorlatilag sohasem használatos. 3 FA1 Ugrás Akkumulátor IR Store Eredmény Load ALU Utasítások Számítás MDR Operanduslehívás Alprogram hívás PC Utasítás lehívás MAR 0.22 Közös sín vagy egysínes rendszer A másik extrém esetként szemlélhetjük a közös sínrendszert. Valamennyi adatátvitel a közös sínen történik. Annak érdekében, hogy lehetővé tegyük az információnak az egyik regisztertől a másikhoz való áramlását, néhány logikai kapura (ki/be kapcsolóra) van szükség, amely lehetővé teszi, hogy egyidőben csak a szükséges regiszterek egyike kapcsolódjon a sínre. A közös sínrendszer előnye, hogy igen olcsó, a hátránya viszont, hgy egyidőben kizárólag egyetlen átvitel lehetséges. Így nincs lehetőségünk arra, hogy párhuzamos műveleteket végezzünk, következésképpen az ilyen típusú számítógép lassú. A közös adat és címsín használata csak a nagyon

egyszerű, célfeladatokra használt processzoroknál alkalmazott. Gyakorlati jelentősége már nincs is Akkumulátor ALU PC IR MDR MAR BelsõCPU-sín 0.23 A többsínes rendszer 4 FA1 A CPU belső sínrendszerének a legáltalánosabb formája a többsínes rendszer, mely egy kompromisszum a fent leírt két extrém eset között. Itt egynél több sín van, melyhez egynél több komponenst illesztünk, néha bizonyos regisztereket - amennyiben szükséges - pont-pont kapcsolattal kötjük össze. A kétsínes belső sínfendszer Egyszerűbb megoldást ad a 2 sínes (adat és címsín) rendszer, amely általánosan elterjedt megoldás a processzorok körében. 2-sínes rendszert alkalmaz: LSI-11, MC68020, I386/486/Pentium; Akkumulátor ALU PC IR MDR MAR Címsín Adatsín A háromsínes belső sínfendszer Nagyobb teljesítményű processzorok esetében az átvitelek gyorsítása érdekében 3-sínes rendszer kialakítása a célszerű, amelynél a címsín mellett

külön adatsín van az írásra és az olvasásra. Ezzel a közel egyidejű írás és olvasás megoldható. 3-sínes rendszert alkalmaz: AM 2900, AM29300, RISC-processzorok. 0.3 Szinkron és aszinkron processzorok 0.31 A szinkron processzorok A szinkron processzornak van egy belső órája. Ez egy elektronikus áramkör, amely rendszeres és pontos időintervallumonként elektronikus impulzusokat generál. Minden lépésnek a műveletet óraimpulzusra kell kezdenie. Bizonyos lépések végrehajtása több, mint egy óraütemet igényel, míg más lépések végrehajtása kevesebb, mint egy óraütemet igényel. Ez viszonylag egyszerű processzor felépítést jelent, de a hátránya, hogy nem minden művelet igényel ugyanolyan hosszú időt, hiába fejeződött már be az előző művelet, a következő addig nem kezdődhet meg, amíg a következő óraimpulzus nem érkezik meg. 5 FA1 óraütem lépésbefejezve A hátránya ellenére a mai processzorok többsége ilyen, pl.

az Intel család A 486 megjelenéséig a PCprocesszorokat úgy tervezték, hogy kétszeres sebességű órajelet kapjanak s minden második órajelet pedig kihagyjanak. Így például egy 386, 25 MHz-es gép tényleges órajele 50 MHz volt A 486-tól kezdve ez megváltozott, most már megegyezik az órajel a processzor frekvenciájával. Például egy 486, 25 MHz-es gépet 25 MHz frekvenciával hajtják meg. 0.31 Az aszinkron processzorok Az aszinkron processzoroknál a következő lépés akkor kezdeményeződik, mihelyt az előző lépés befejeződött. Ezáltal ez kiküszöböli a processzornak a következő órajelre való várakozását, következésképpen a processzor sebességének növekedését kell, hogy maga után vonja. Egyébként ezt az eredményezi, hogy egy extra logikai áramkör van beépítve, amely érzékeli minden esemény végét. Hátránya: az extra áramkör az aszinkron processzort drágábbá teszi (ez a lépés végét érzékelő logikai áramkör ára

magasabb, mint az egyszerű órajel áramkör); az esemény végének az érzékelése bizonyos időt igényel, és ez csökkenti a szinkron processzorhoz viszonyított időmegtakarítést. lépésbefejezve lépésvégeérzékelve, új lépéskezdete Az aszinkron üzemmódú CPU egyébként általában gyorsabb, de bonyolultabb és drágább, mint a szinkron üzemmódú. 1. Műveletvégző egység Részei: 1. 2. 3. 4. regiszterek adatutak (a címsín itt már nincs értelmezve!) kapcsolópontok a szűkített értelemben vett ALU 1.1 Regiszterek Gyors hozzáférésű átmeneti tárolók, mely a műveletvégző egységen belül helyezkedik el. Ebben adatokat tárolhatunk, elérésük gyors. Lehet engedélyezni vagy tiltani az írást: van vezérlője A regisztereket két csoportba sorolhatjuk: - az egyik csoport már a logikai architektúrában szerepelt: programozható regiszterek (szabadon felhasználhatók). A CPU főbb építőelemei - köztük a programozható regiszterek - a

következők: - "rejtett" (belső) regiszterek (a felhasználó nem látja őket. Pl mindenféle puffer-regiszter) Ezt nézzük meg a következő példákon keresztül: 1.2 Adatutak 6 FA1 Vizsgáljuk meg a műveletvégző egységen belüli adatutakat. Ezek az építőelemek a legkülönfélébb módon kapcsolhatók össze és szervezhetők. 1.11 Adatút csatolási módok 1.111Egy adatutas: Ebben az esetben az ALU és a CPU valamennyi regiszterét egyetlen közös adatút köti össze. Ezt nem szabad összekeverni az adatsínekkel, amelyek a CPU-t a memóriával és az I/O egységekkel kötik össze. A három külső sínt (adat - MDR, cím - MAR, vezérlő - control) az ábra a memóriával kapcsolatosan tartalmazza. Az R0-Rn regiszterek száma és funkciója gépenként változó. Ezek lehetnek általános célú regiszterek a programozó számára, de egy részük lehet dedikált, speciális célú regiszter is, mint az index vagy a stack regiszter. A két SRC0 és

SRC1 regisztert korábban nem említettük. Ezek a programozó számára transzparensek Viszont a programozónak számításba kell venni a létezésüket, bár sohasem hivatkozhatunk rájuk közvetlenül egyetlen utasításban sem. Ezeket csak a CPU használja ideiglenes (temporary) tárolásra bizonyos utasítások végrehajtása során. Egyébként sohasem használatosak az egyik utasítás által generált adat más utasítás által történő későbbi hasznosításra. Vizsgáljuk meg az előző példát: ADD R0,R1 (R0:=R0+R1) R0 R1 Rn SRC1 SRC0 ALU RSLT A végrehajtás hipotézisa: 1. 2. 3. 4. SRC0 ←R0 SRC1 ← R1 RSLT ←R0+R1 R0 ← RSLT Előnye. olcsó Hátránya: nincs párhuzamos műveletvégzés 1.112 Két adatutas: 7 FA1 Az egy adatutas megoldás csupán a CPU építőelemeinek egy lehetséges összekapcsolási formáját adja. Egy alternatív megoldás a két adatutas. Valamennyi regiszter outputot az A adatúthoz, s az összes regiszter inputot pedig a

B adatúthoz csatlakoztatják. R0 R1 . Rn SRC1 SRC0 ALU RSLT regiszter output regiszter input A végrehajtás hipotézisa: 1. 2. 3. 4. SRC0 R0 SRC1 R1 RSLT R0+R1 R0 RSLT Az előző utasítás 4. lépése és az aktuális utasítás 1 lépése párhuzamosan folyhat Előnye: gyorsabb Hátránya: drágább 1.113 Három adatutas: Ekkor szakosodott adatutak: 2 db regiszter output adatút 1 db regiszter input adatút 8 FA1 R0 R1 Rn SRC0 SRC1 (pl. PDP11/45) ALU RSLT A végrehajtás hipotézisa: 1. 2. 3. 4. SRC0 ← R0 SRC1 ← R1 RSLT ← R0+R1 R0 ← RSLT Az előző utasítás 4. lépése és az aktuális utasítás 1 és 2 lépése párhuzamosan folyhat Előnye: gyorsabb Hátránya: drágább A fizikai folyamatra nem tudunk hivatkozni a programból. Megvalósításuk multivibrátorral (flipfloppal); Típus: RS, VK, D, T; élvezéreltek vagy szintvezéreltek 1.3 Kapcsolópontok A sín nem megosztható eszköz. Egy sínen egy időben

csak egy adó lehet Ha kettő, a bitek ütköznek Egy sínre több egység kapcsolódik. A rávezető és az onnan elvezető vonalban van egy-egy kapcsoló, melyek feladata: egy időben az adatúton csak egyetlen egy lehet nyitva. 9 FA1 A kapcsoló természtesen nem fizikai, hanem tranzisztor. Három állapotú 0 1 Z, amikor adat nem folyhat át rajta. A regiszter output kapuja képes arra, hogy a regisztert elektronikusan lekapcsolja az adatútról, vagy pedig 0-át vagy 1-et helyezzen az adatútra. Mivel ez három lehetőséget támogat, az ilyen kaput háromállapotú kapunak nevezzük Önálló input-vezérlés is van, ami lhetővé teszi, hogy a regiszter elektronikusan le legyen kapcsolva az adatútról illetve az adatútról 0-át vagy 1-et fogadjon. A kapcsolópontok általában a regiszter részét képezik. 1.4 ALU Akármilyen parancssort nézünk meg, valami mindig közös: az összeadás végrehajtása. Ez annyira elemi operáció, hogy nélküle nem lehet meglenni.

(Tulajdonképpen kizáró vagy-okkal meg lehet csinálni az összeadást, csak nagyon macerás. Két bitet még csak-csak össze tudnánk adni, megcsinálhatnánk a carry-átvitelt, majd a három érték összeadását. Ha mindezt feltupírozzuk előjelek kezelésével, már túl bonyolult. Tehát mindez helyett inkább az összeadás az elemi művelet Az összeadás jelentőségét növeli, hogy több, más műveletnél, így a szorzásnál is szerepel, mert összeadásra vezetjük vissza. 1.41 Fixpontos műveletek 1.411 Normál bináris kódú pozitív számok összeadása Egybites félösszeadó Maga a bináris összeadás: A 1 B 1 C 10 átvitel összeg Két egybites normál bináris kódú szám összeadását egy kétbemenetű és kétkimenetű kombinációs hálózattal végezhetjük. Σ 2 A B S C A két összeadandó bit az A és a B bemeneten érkezik. Az S (summa) kimeneten jelenik meg az összeg, a C (carry) kimeneten pedig az esetleges átvitel. A hálózat

működését a bináris összeadás szabályainak figyelembevételével a következő igazság táblázat írja le: A 0 0 1 1 B 0 1 0 1 S 0 1 1 0 10 C 0 0 0 1 FA1 Ez alapján felírhatjuk a kimenetekre vonatkozó logikai függvényeket, s realizáljuk ezt kapukkal: S=AB+AB= A ⊕B C=AB =1 A S B & C Ezt azért nevezzük félösszeadónak, mert két bináris számot összead ugyan, de mi van a bejövő carryvel? A félösszeadó jelölése: ∑/2 Az egész összeadó: határozzuk meg az összeget, majd adjuk hozzá a carry-t. Teljes összeadó 2 db ∑/2-ből Cin X Y S Σ 2 S' C' Σ 2 C'' 1 C out S' - csak részösszeg C' és C'' - csak részt-carry Teljes összeadó Általában egy kombinációs logikai áramkörrel valósítják meg. Az operandusokat az ALU számára két regiszter outputjaként biztosítják a belső sínen keresztül. Az eredményt általában egy másik regiszterhez csatlakoztatják, mihelyt a

konbinációs áramkörök azt végrehajtották. Általában az ALU művelet gyorsabb, mint a memória-elérési művelet. Ez azt jelenti, hogy egy olyan utasítás, amely ALU műveletet jelent olyan operandusokon, amelyeket a memóriából kell kiolvasni, nem igényel számottevően több végrehajtási időt, mint az utasítás, amely csak a memória egyik helyéről átmozgatja az információt a memória másik helyére. 11 Σ A S FA1 Cout B Cin Igazságtábla A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Cin 0 1 0 1 0 1 0 1 S 0 1 1 0 1 0 0 1 Cout 0 0 0 1 0 1 1 1 A logikai függvények felírása A Cin helyett egyelőre csak sima C-t írva írjuk fel a logikai függvényeket: S=ABC + ABC + ABC + ABC Cout=ABC + ABC + ABC + ABC Azonos átalakítások Hajtsunk végre azonos átalakításokat a következő célfüggvénnyel: minimalizáljuk a szintek számát (azaz a végrehajtási időt); csökkentsük az elemszámot (strukturális egyszerűsítés és költségmérséklés);

Ennek során használjuk fel a Boole-algebra néhány alaptételét: A+A=A AB+AB=AB A+A=1 [1] [2] S=(AB+AB)C + (AB+AB)C A⊕B A⊕B Levezetés (miért tudjuk az első zárójelet átalakítani?): ( )( ) A ⊕ B = AB + AB = AB∗ AB = A + B A + B = AA + AB + AB + BB = AB + AB X=A⊕B S=XC+XC=X⊕C=A⊕B⊕C (3) Ha kapukkal realizáljuk, fontos: a kizáró vagy csak két operandus között van értelmezve, ezért három kaput ne rajzoljunk fel. A megoldás: kettőt felrajzolunk s az outputja meg a harmadik A [2] alapján: abc=abc+abc+abc Ezt behelyettesítve a következőt kapjuk: Cout=ABC+ABC+ABC+ABC+ABC+ABC A következő Boole-algebra tétel alapján egyszerűsíthetünk: A+A=1 Cout=BC(A+A)+AC(B+B)+AB(C+C) Cout=BC+AC+AB=AB+(A+B)Cin A carry-nek tehát két része van. az AB, melyben a befolyó carry nem szerepel, tehát független tőle; s a másik pedig függ tőle. Megvalósítás Realizáljuk kapukkal a kapott logikai eredményeket: 12 (4) FA1 S=a ⊕ b ⊕ c: =1 A =1

S B C (3) Cout=AB+(A+B) Cin & A B A 1 C out 1 B & C (4) Az összeadás időszükségletének kiszámításhoz figyelembe kell venni az egyes logikai kapuáramkörök jel-késleltető hatását és a "leghosszabb út" áramköreinek a számát. Ez egy háromszintű hálózat Amennyiben a C-re kapott másik alakot valósítjuk meg, akkor kétszintű hálózatot kapunk. Ezt szeretjük inkább: Cout=AB+AC+BC 13 FA1 A & 1 B A & Cout C B & C (3) A megvalósított egység tesztelése Amennyiben a megvalósított egység nem az elvárt módon működik, akkor ismét el kell végeznünk az azonos átalakításokat és a költséges megvalósítást. Ha viszont bármilyen apró módosítást, továbbfejlesztést szeretnénk rajta végrehajtani, akkor vissza kell mennünk egészen az igazságtábláig. Tehát a módszer hátránya a nagyfokú erevsége és a hardver-megvalósítás okozta költségessége. Így elkészült az egybites

teljes összeadónk, a gyakorlatban azonban ritkánvan szükségünk két bit öszeadására, mivel a bináris számokat általában n-bite regiszterekben tároljuk. Hogyan csinálunk tehát a regisztereket is kezelni tudó n-bites összeadót? n-bites soros összeadó Az összeadandó két szám, A és B megfelelő bitjeit a legkisebb helyiértékűtől kezdve ráadjuk az összeadó bemeneteire. A minden egyes egybites összeadás eredményeképpen keletkező carry-t egy flipflop tárolja és a következő egybites összeadás során inputként fog szerepelni A soros összeadó tehát az operandusokat a legalacsonyabb helyiértéktől kezdve bitenként egymás után összeadja. Más szavakkal: az első lépésben összeadja a két operandus 0 bitpárját, utána az 1 bitpárját, vagyis az összeadás "jobbról balra" - a növekvő bináris helyiérték irányába - halad. Világos, hogy egy összeadási műveletet annyi lépésben végez el, ahány bitesek az operandusok.

Ha a két összeadandó szám hossza nem egyezik meg, akkor a lépésszámot a hosszabb parancs határozza meg, ugyanis a gép ilyenkor automatikusan kiegészíti a rövidebb operandust értéktelen, ún. vezető nullákkal Az elrendezés legfontosabb része az egybites teljes összeadó. Ennek a felépítését már ismerjük Működését a következő példával szemléltethetjük. Figyelmet érdemel az a körülmény, hogy a soros összeadóban csupán egyetlen összeadó van. Az A és B operandust egy-egy önálló regiszterben tároljuk a munkavégzés kezdetéig. Ez más szavakkal azt jelenti, hogy az összeadás megkezdése előtt ezt a két regisztert fel kell tölteni a megfelelő operandusokkal. A regisztereket úgy alakítják ki, hogy alkalmas vezérlőjelek segítségével tartalmukat egy bittel jobbra lehet léptetni. Az összeadás az alábbi módon megy végbe: 14 FA1 carry A B Σ léptető-regiszter léptető-regiszter S Cout 1 Cin tároló vagy 1-bites

késlel-tető az első léptetőjel hatására az A és a B legalacsonyabb helyiértékű (jobbszélső) bitje belép az egybites teljes összeadóba, amely az S kimenetén a helyes részösszeget, a Cout kimenetén pedig az esetleges átvitelt szolgáltatja; az S részösszeget közvetlenül visszavezetjük az A helyére. Az első lépés befejeződése után tehát a felső regiszter legfelső bitje már nem az A operandushoz, hanem a végeredményhez tartozik; az egy bites teljes összeadóhoz csatolt tároló addig tárolja a Cout átvitelt, amíg esedékessé nem válik a következő bitpár összeadása. Ekkor a teljes összeadó a már megismert módon hozzáadja az átvitelt az aktuális "félig kész" részösszeghez. Az összeadó működését tanulmányozva fontos következtetést vonhatunk le, hogy milyen információ vész el illetve őrződik meg az összeadás során. Mivel az A operandusunkat az eredmény felülírja, az összeadás elvégzése után az A

itt többé nem áll rendelkezésünkre. A B operandust azonban lépésenként visszavezetjük saját korábbi helyére, ez tehát ismét felhasználható. Tulajdonképpen A sem veszett el véglegesen, hiszen megtalálható az operatív tárban vagy másik regiszterben, vagy pedig valamilyen háttértárolón. Ahhoz azonban, hogy az A-t valamilyen aritmetikai műveletben szerepeltessük, újból be kell töltenünk az ALU által látott valamelyik regiszterbe. - Abban az esetben, ha a teljes összeadó és a flip-flop műveletvégzési időigényét sorrendben d és a D-vel jelöljük, akkor az n-bites összeadás időigénye n(d+D) lesz. Meg kell jegyezni egyébként, hogy a szükséges áramkör mennyisége az n-től független. T∑=n(d+D) vagy T∑=nt Ez a min. összidő, ennél csak hosszabb lehet a rezsi-időket is figyelembe véve Hogyan tudunk gyorsítani? a d értékét csökkentjük: igen gyors kapukat alkalmazva. Egy lassú kapu 20 nsec-os, ennél inkább gyorsabbak;

bit-helyiértékenként párhuzamosan hajtjuk végre az összeadást. 15 FA1 n-bites párhuzamos összeadó (ripple adder - terjedő vagy végighullámzó összeadó) An-1 Bn-1 Σ Cout Sn-1 B2 A2 Σ Cn-2 B1 A1 Σ C2 S2 0101 1010 1111 <---- 0 C1 B0 A0 Σ S1 C0 Cin S0 Példa 1 Példa 2 Végrehajtási idő τ 2τ 3τ 4τ Művelet 0101 1010 1110 1100 1000 10000 Átvitel (carry) Művelet leírás <---- 1 elkészült a párhuzamos összeg elkészült a c1 carry elkészült a c2 carry elkészült a c3 carry A valamennyi n bit-párt szimultán módon összeadó áramkört párhuzamos összeadónak nevezzük. Egy egyszerű párhuzamos összeadót kialakíthatunk n db teljes összeadóból. Minden egyes teljes összeadó fokozat balról egy carry bemenetet tartalmaz. Könnyen belátható, hogy a vázolt módon a párhuzamos összegzéshez annyi idő szükséges, amennyi idő alatt a legkisebb helyiértéken keletkező átvitel (carry) hatása el tud jutni

a legnagyobb helyiértékig. Az összeadandó számok változása után ugyanis az Si kimeneten mindig tranziens változás játszódik le, amíg minden egyes Ci-1 bemenet értéke nem állandósul. Ez a legnagyobb helyértéken következhet be legkésőbb. A legkedvezőtlenebb esetben ugyanis minden helyiértéken történhet változás a keletkező átvitel értékében. A maximális összeadási időigény tehát nd, ahol d egy teljes összeadó fokozat időigénye. Láthatjuk, hogy nagy mennyiségű többlet-áramkörrel ugyanazt az időeredményt értük el, mint a soros összeadónál, azaz az időszükséglet a bitek számával (n) lineárisan nő. Tehát a ripple-carry adder (terjedő vagy végighullámzó átvitel) esetén hiába végeztük el ugyanis magát a bit-összeadást párhuzamosan, időt mégsem nyertünk. A gyors összeadó tervezésének általános stratégiája, hogy csökkentsük azt az időt, ami a carry terjedéséhez szükséges. "Szimultán"

átvitelképzés vagy carry look-ahead vagy rekurzív módszer Mit lehet tenni? Használjuk azt az összefüggést, amelyből a (4) ábrát kaptuk: Cout=AB+(A+B)Cin 16 FA1 A carry tehát független az előző helyiértéken képződő carry-től, kizárólag a befolyó operandusoktól és a kívülről beérkező átviteltől függ. Mindent tehát előre ismerünk, hisz a mindhárom forrásadat előre ismert és az összeadás végrehajtása megkezdésekor már a rendelkezésünkre áll. AB bitcsoport = G (Generate: a carry-t generáló bitcsoport A+B bitcsoport = P (Propagate: a carry-t terjesztő bitcsoport) Tehát az összefüggésünk új alakja: Ci= Gi + Pi Ci-1 C0=G0+P0*Cin C1=G1+P1*C0=G1+P1(G0+P0Cin) C2=G2+P2*C1=G2+P2(G1+P1(G0+P0Cin)) C3=G3+P3(G2+P2*(G1+P1(G0+P0Cin))) Cn-1=Gn-1+Pn-1(Gn-2+Pn-2*(Gn-3+Pn-3(.))) Ez akkor lesz jó, ha elvégezzük a kijelölt műveleteket: C2=G2+P2G1+P2P1+P1G0+P2P1P0*Cin C3=G3+P3G2+P2G2+P3P2G1+P3P2P1G0+P3P2P1P0*Cin Akármennyire fejtem is ki,

mindig lesznek benne szorzatok s azokat kell összeadni s ez együtt kettő kapumélység. Ehhez jön a P és G meghatározásához szükséges további kapumélység, tehát összesen 3 kapumélység, azaz a carry-lookahead összeadó teljes ideje 3d: Tn=3d A 1 P B A B & 3 G 2 & & 1 C & 17 3 FA1 Több emitter: kollektor emitter Max. 16 bemenetet gyártanak, nem fér el több emitter Ezért 4 vagy max 8 emitter Ez a CLA - carry look ahead (gyors átvitel előrejelzés) összeadó. A következőképpen valósítható meg: Mivel a carry-generáló egyenletek összetettsége a fokozatok számával nő, ezért gyakorlati megfontolásokból a carry-lookahead fokozatok száma kisebb nyolcnál. A CLA áramkörök architekturális elhelyezkedése Összeadó+carry look ahead (gyors átvitel előrejelzés) Az átvitelgyorsító (CLA) az átvitel értékét az összeadandó számok bitjeiből és a Cin-ből még az összeadás elvégzése előtt, minden

helyértéken egyszerre állítja elő. CLA Cn-2 A n-1 B n-1 C1 C2 A out A 2 Sn-1 Cn-2 C 2 B1 1 A S 2 C 1 B 0 0 C S S S S C B 2 C0 S 1 C 0 S 0 A carry-k továbbra is képződnek, csak nem használjuk őket semmire, mert igen lassan jönnek létre. P és G előállítás az összeadókban A gyakorlatban alkalmazott másik módszer szerint minden egyes teljes összeadónak a ci carry output vonalát helyettesítik a két carry generate gi és propagate pi jelt előállító áramkörrel. 18 in FA1 CLA Cout P P G P G P C in G S S S S G Két kapuval többet tesznek be a tokba, ennek nincs semmi akadálya. Itt a művelet három lépésben zajlik: 1. az összeadókban bit-helyiértékenként párhuzamos összeadás valamint P és G képzés; 2. a CLA-ban előállítjuk egyszerre az összes carry-t: 3. az összeadókban bit-helyiértékenként párhuzamosan hozzáadjuk a kapott összegekhez a carryket. (saját elképzelés) Hosszú

operandusok esetén csoportképzés Egy darab CLA 8-bites, hogy 32-bites szót tudjunk feldolgozni, négyet veszünk belőle. Cout Cout Cout C in Minden jó. de a carry sorosan terjed a 8-bites egységek között Ezért eggyel magasabb szintre hozzárendelünk egy ugyanolyan carry előrejelzőt. Cout CLA Áramkörileg a két fölső szint teljesen megegyezik. Gyakorlati IC-példák a Fodor Tamás: Digitális szgépek 183. oldalán! Három szám összeadása (carry-save adder - carry-megtakarító összeadó Néha szükség van rá, hogy kettőnél több operandus összeadását egyetlen lépésben végezzük el. Ennek szokásos eszköze az átvitel-megtakarító (carry-save) összeadó, amelynek elve, átvitel-végigfutást csak akkor hozunk létre, amikor már kettőre redukáltuk az operandusok számát. Általánosságban n operandus esetén az áramköröknek n-1 emelete van. Minden emelet áramköri készlete azonos, és egyébként alkalmas lenne két operandus

összeadására, de a megszokott, végighullámzó átvitelképzést csak a legalsó emeleten találjuk meg. ábra: Sára: 76. oldal 19 FA1 Z=W+X+Y w x 3 w 3 2 x S Z5 c S C S 3 Z Z4 2 C 2 S S S 1 C Z 1 Z 1 1.412 Fixpontos kivonás A kivonás művelete az összeadáshoz hasonlóan végezhető el, ha biztosítjuk, hogy a kisebbítendő helyére a nagyobb, a kivonandó helyére pedig a kisebb szám kerüljön. Ellenkező esetben ugyanis az eredmény nem lesz helyes, ha bitenként formailag helyesen is végezzük el a műveletet. A kivonás megkezdése előtt tehát a két számot össze kell hasonlítani és ennek eredményétől függően kell azokat beírni a megfelelő regiszterekbe. A párhuzamos és soros kivonás ezek után ugyanúgy valósítható meg, mint az összeadás. A kivonó hálózatok természetesen módosulnak az elvégzendő műveletnek megfelelően. Itt is felépíthetjük az igazságtáblát, megállapíthatjuk az eredmény megkapása

érdekében végrehajtandó logikai függvényt, az azonos átalakítások eredményeit pedig kapukkal realizálhatjuk. Az aritmetikai műveleteket a számítógépben előjeles számok között kell végezni. Ezért az ismertetett eljárásokkal nagyon gyakran kellene komparációt végezni és ettől függően összeadást vagy kivonást végezni. Ennek elkerülésére célszerű az előjeles számokat olyan kódban ábrázolni, amely lehetővé teszi, hogy az aritmetikai alapműveleteket - így a szorzást és osztást is - az előjeltől függetlenül összeadási lépésekre vezessük vissza. Így a számítógépben csak az összeadás műveletét kell megvalósítani és az összeadó hálózatot megfelelőképpen vezérelni. Az ALU-ban tehát valójában csak az összegző hálózat végez igazi aritmetikai feladatot, a többi művelet az összeadási lépések megfelelő összeállítása révén valósul meg. Sokfajta kódolási módszer létezik, ezek közül csak kettőt

veszünk, az egyes és a kettes komplemens szerinti ábrázolást. Inverz kód vagy egyes komplemens A hagyományos módszer a fixpontos kivonásra, hogy a kisebbítendőből kivonjuk a kivonandót. Pl +13 -(+7) 1101 0111 20 (+7) 0 S Az első lépcsőben keletkező carry-ket nem vezetem végig, hanem a második lépcsőbe vezetem be összeadandóként. A B x 0 y1 S Z 2 3 w S S S3 4 x 1 1 y2 y3 0 w 2 0 0 FA1 +6 Ezt a módszert már elvetettük. Helyette képezzük a kivonandó egyes komplemensét, s adjuk hozzá a kisebbítendőhöz. Ha a szám pozitív, akkor a komplemense önmagával azonos. A szám előjelét jelezzük az elé írt 0-val vagy 1-sel, attól függően, hogy a szám pozitív-e vagy negatív. Így előjelbites egyes komplemes számot kapunk. Az előjelbitet a többi bittel azonos módon kell kezelni, így az eredményben keletkezett előjelbit szintén helyesen jelzi az eredmény előjelét. Ha az eredmény negatív, akkor az előjelbitje 1

és az abszolút értéke az egyes komplemens képzés útján állapítható meg. A 7 egyes komplemense, az előjelbittel együtt: 11000 (-7) A B 13 +(-7) 01101 11000 100101 (+5) Az eredmény nem helyes. Különböző megfontolásokból a legnagyobb helyiértéken keletkező átvitelt adjuk hozzá a legkisebb helyiértékhez: 100101 1 (5) (1) (6) 00110 Megállapíthatjuk tehát, hogy kivonás helyett összeadással is eljuthatunk a végeredményhez, ha a negatív számokat (kivonandókat) egyes komplemens kódban ábrázoljuk és az eredményt az említett átvitel-visszacsatolással módosítjuk. B Trans A Cout S Eredmény =1 OVF EzaC C carrymegragadása i-1 i OVF=túlcsordulás Ez képes az A-B-re. Két multiplexer kell a B-A-hoz: 21 Cin FA1 Ha A+B-t is tud, az lesz a tökéletes. Vezérelhetnénk, hogy most invertálja-e a B értékét vagy sem Erre a legjobb a kizáró vagy. input a vezérlőláb 0 0 1 1 output c 0 1 1 0 b vezérlőláb 0 1 0 1 Ha a

vezérlőláb 0, akkor átengedi egy az egyben, ha pedig 1, akkor invertál. Milyen műveletet kell elvégeznünk ahhoz, hogy e funkciót tejesítse? Ez pont a kizáró vagy. A TRANS egység: Bbitjei =1 =1 =1 =1 x3 x2 x1 x0 Vezérlés (+/-) 0/1 Túlcsordulás Bármilyen is a számábrázolás, előfordulhat, hogy egy aritmetikai művelet eredményeként olyan számot kapunk, amely nem ábrázolható annyi helyiértéken, amennyi az adatszóban rendelkezésre áll. Ebben az esetben a kapott eredmény természetesen nem helyes, ezért ezt az ALU-nak jeleznie kell. Ezt a jelenséget túlcsordulásnak nevezzük. OVF = Ci ⊕Ci-1 A legnagyobb helyiértékből kifolyó és a legnagyobb helyiértékbe befolyó carry kizáró vagy kapcsolata. Összeadok két pozitív számot és negatívot kapok vagy összeadok két negatív számot és pozitívat kapok, akkor van túlcsordulás. Tehát összeadás esetén csak azonos előjelű operandusok esetén értelmezett a túlcsordulás. Pl.

(az első bit az előjel) 22 FA1 0100 0110 1010 0 ⊕ 1 = 1: van túlcsordulás pozitív pozitív negatív 100 101 001 negatív negatív pozitív 1 ⊕ 0 = van túlcsordulás 110 111 101 1 ⊕ 1 = nincs túlcsordulás A túlcsordulás megjelenését fontos, hogy felfedezzük a számítógépen. Szokásos, hogy ennek jelzésére egy flag-et szentelnek indikátorként. Amikor egy összeadási vagy kivonási művelet túlcsordulást eredményezett megszakítás következhet be. A programozó feladata, hogy eldöntse a foganatosítandó cselekedeteket. Kettes komplemens kód (KKK) A legkisebb helyiértéken az egyes hozzáadását a kettes komplemens képzésekor a művelet előtt hajtjuk végre. Így a legnagyobb helyiértéken keletkező átvitelt nem kell visszacsatolni, hanem figyelmen kívül hagyható. Végezzük el a korábbi feladatot kettes komplemens vonatkozásában is. A 7 kettes komplemense, az előjelbittel együtt: 11001 (-7) A B 13 +(-7) 01101 11001 100110 (+6)

Az egyes komplemes-képzéshez képest két különbség: az egyes komplemens képzés helyett mindenütt kettes komplemens képzést kell alkalmazni; nem kell az eredményt átvitel-módosítással korrigálni. A 13 01101 B+(-7) 11000 100101 vezérlés 1 eredmény (5) (1) (6) 00110 B Vezérlés input: összeadáskor 0, kivonáskor 1 A Cout Trans Σ Eredmény 23 Cin FA1 A vezérlőkód 1-ét bevezetjük Cin-ként s így az eredő: kettes komplemens kód képzés. Többletes kód Kevés van róla Fodor: 181. oldal feladataiban 1.413 Fixpontos szorzás A szorzás és az osztás jóval komplexebb művelet, mint az összeadás és a kivonás. A végrehajtási idejük jóval lassúbb, mint az egyszerű összeadás, MOVE, stb. Ennek oka, hogy a megvalósításuk során az ALU-ban egy összeadási - kivonási - léptetési sorozat zajlik, amit a mai gépeken mikroprogram vezérel. A nagyteljesítményű gépeken hardver úton megvalósított szorzókat és osztókat használnak,

hogy növeljék az aritmetikai műveleti sebességet. Mivel az ADD, SUBTRACT és SHIFT elérhető gépi utasítás formájában, ezért mind a szorzást, mind pedig az osztást meg lehet valósítani szoftver úton, program-eljárás segítségével. Tehát öszefoglalva: olcsó gép közepes gép gyors, drága gép gépi kódú eljárás mikroprogram áramköri szorzó és osztó Szorzási algoritmusok, nemnegatív számok szorzása a) a szorzó legkisebb helyiértékű jegyével szorzok, majd a szorzatot balra eltolva összeadom. C=A*B 13x123 39 26 13 1599 b) algoritmikusabb: ciklikusan ismételve a szorzást és a részletszorzatnak egy gyűjtővel való összeadását 13x123 0000 39 0039 260 299 1300 1599 ez egy gyűjtő (használat előtt kinullázandó) c) nem szorzással, hanem eltolással valósítjuk meg az előzőt: 13x123 0000 az algoritmus: 39 szorzás 0039 összeadás 26 léptetés 299 s ezt annyiszor végezzük, ahány jegye van a szorzónak 13 1599 Bináris

műveletvégzés 24 FA1 Az algoritmust tehát annyiszor hajtjuk végre, ahány jegye van a szorzónak. Mivel bináris számokkal számolok, a szorzó eleve hosszú, jóval hosszabb, mint a decimális esetén. Ennek következményei: A szorzás időigényessége, a bináris szám hossza: Láthattuk, hogy a szorzás ciklusmagját annyiszor ismételjük, ahány jegye van a szorzónak. Hasonlítsuk össze a decimális és a bináris szám hosszát: A decimális helyiértékek száma 1 2 3 Példa A bináris helyiértékek száma 4 7 10 9 99 999 Példa 1001 1100011 11011001001 Tehát a „Szorzási algoritmusok”-nál alkalmazott háromjegyű, 123-as szorzó binárisan tíz számjeggyel írható fel, így a ciklus három helyett tízszer fut azaz több időt vesz igénybe. Ez rögtön rámutat a szorzás jelentős időigényére is, hisz végső soron elméletben annyi szorzást összeadást hajtok végre, ahány egyes van a szorzóban, s annyi léptetést, ahány jegyű a

szorzó. A szorzat hossza A szorzás elvégzésekor az eredmény max. kétszerese az operandusok hosszának Vizsgáljuk meg a példánkat: Operandusok A B C Példa A decimális helyiértékek száma 1 1 2 1 2 2 2 3 4 9x9 9x99 99x99 Általános forma (helyiérték) m n max. m+n A bináris helyiértékek száma 4 7 max. 11 A szorzat keletkezése két regiszterben Maguk az operandusok szóhosszúságúak. Architekturálisan a regiszterek az adatszó hosszával egyeznek meg, a fenti szabálynak megfelelően az eredményt befogadó akkumulátornak (vagy más e célra használt) regiszternek kétszeres hosszúságúnak kellene lennie. Az algoritmust tehát annyiszor hajtjuk végre, ahány jegye van a szorzónak s miután valamelyikkel szoroztam, utána már nincs rá szükségem. A feleslegessé váló szorzó-jegyek helyén tároljuk el az eredménynek már lépésenként elkészülő eredmény-helyiértékeit (ezek már ki vannak shiftelve, nem vesznek részt az összeadási

műveletben). Példaképpen nézzük meg a fenti esetben a szorzó és az eredmény kisebb helyiértékeinek változását, feltételezve, hogy három jegyű a szóhosszam. 1 2 3 9 1 2 9 9 1 5 9 9 A szorzat nagyobb helyiértékei (adott példában az 1) a szorzat nagyobb helyiértékei számára kijelölt regiszterben képződnek. Előjeles számok szorzása (soros szorzók) 25 FA1 Ábra és leírás: Gál II. kötet 26-27 oldal) A számok abszolút értékes kódban vannak az abszolút érték előállítása az előjel eltávolításával, eredmény előjel (signum) meghatározása: S=S1 ⊕ S2 elvégezzük az előjel nélküli szorzást; visszaállítjuk a helyes előjelet. A módszer egyértelmű, a macerás csak: az előjel levágása és az új előjel visszaállítása A számok kettes komplemens kódban vannak Az algoritmus a nem inverz (egyenes) kódhoz hasonló, a különbség csupán annyi, hogy amikor a szorzó legmagasabb helyiértékű bitjével szorzunk,

akkor a részletszorzatot nem hozzáadjuk, hanem levonjuk a részletösszegből. A kettes komplemens kódú ábrázolás úgy is tekinthető, mintha a legmagasabb helyértékű bit súlyozása negatív, a többié pedig pozitív lenne. Mivel azonban a szorzandó maga is lehet, hogy negatív szám, a részletösszeg jobbra léptetésekor az előjelbitre különös tekintettel kell lennünk, azaz a korábbi előjelbitet jobbra léptetjük, ugyanakkor a legmagasabb pozícióban változatlanul megismételjük ("csíkot húz maga után"). A szorzás gyorsítása Bit-csoporttal történő szorzás A szorzónak egyidejűleg nem egy, hanem több, például két egymás melletti jegyét vesszük figyelembe és egy-helyiértékes léptetés helyett több helyiértékes léptetést végzünk. A szorzó egymás melletti két bináris jegye 00, 01, 10 vagy 11 lehet: • 00 esetén nem kell a szorzandót a részösszeghez hozzáadni, csak kettőt léptetünk balra; • 01 esetén a

szorzandó egyszeresét adjuk hozzá, majd kettőt léptetünk balra, • 10 esetén a szorzandó kétszeresét (egy helyiértékkel balra tolt értékét) adjuk hozzá, majd kettőt léptetünk balra • 11 esetén a szorzandó háromszorosát kell a részösszeghez hozzáadni, majd kettőt léptetünk balra Az utóbbi esetben már másképpen csinálják: néggyel szoroznak, majd kivonják belőle a szorzandó egyszeresét, így gyorsabb. A magyarázatot lásd a Booth-féle algoritmusnál Példa A feladat kijelölése (7x9)D =63 (0111x1001)B A részlet-számítás (a szorzandó kétszeresének meghatározása) eltolással összeadással 0111 = 7D kettővel való 0111 szorzása megfelel az +0111 1110 eggyel balra léptetésének: 1110 = 14D azaz 7+7=14 (igen gyors) (viszonylag lassú) Maga az összeadás 0111x1001 0000 0111 0111 1110 111111 7x9=63 Az összeadás lépései tehát: 1. 2. hozzáadom a kinullázott gyűjtőhöz a szorzandó egyszeresét, majd kettőt léptetek balra

meghatározom a szorzandó kétszeresét, majd hozzáadom 26 szorzás 01-gyel szorzás 10-val FA1 A hárommal való szorzás helyett már másképpen csinálják: néggyel szoroznak, majd kivonják belőle a szorzandót, így gyorsabb. Ezzel már előre is siettünk a következő gyorsítási lehetőségre Booth-féle algoritmus Azért lassú egy szorzás, mert sok 1-es van a szorzó bitjeiben s ez sok összeadást jelent. Az algoritmus próbálja dekomponálni (trükkösen átalakítani) úgy, hogy kevesebb egyes legyen benne. Nem működik minden számra. Azoknál jó, ahol hosszú, csupa egyes vagy csupa nullás csoportok vannak A konkrét algoritmus helyett az elv: Például 62-vel kell szoroznunk. 0011|1110 = 62 Mivel 5 db egyest tartalmaz, ez 5 db egységnyi műveletet eredményez (az összeadást tekintve egységnek) Gyorsítás: 62 közel van a 64-hez 64-2= 26-21 Így a szorzandót megszorzom 64-gyel, majd kettővel és veszem a két eredmény különbségét: 0100|0000

-0000|0010 64 -2 A binárisan végzendő műveletek: • hatszoros léptetés balra; • a egyszeresének hozzáadás a gyűjtőhöz; • egyszeres léptetés balra; • a szorzandó egyszeresének hozzáadás a gyűjtőhöz; • a két eredmény kivonása egymásból. Mivel a léptetés rendkívül gyors, tehát összesen 2 db összeadást, majd 1 db kivonást végzek, ami 3 db egységnyi műveletet jelent. Az eredeti megoldással szemben 40%-os gyorsítást sikerült elérnünk! Az egzakt algoritmus helyett az elv: 0011|1110 = 62 ez közel van a 64-hez 64-2= 26-21 Tehát hatszoros léptetés balra, egyszeres léptetés balra: 0100|0000 -0000|0010 64 -2 Tehát ez azt jelenti, hogy összesen két szorzást végzek, majd egy kivonást csak. C=AxB C=A(X-Y) C=AxX-AxY B=X-Y 011000000 000000110 0|01100|0000 1|11111|1010 1|01011|1010 27 FA1 62x3= 186 128+58= 186 0 1 -1x súly 1 0 +1x súly 13 01101 -6 11010 átkódolás: 0 -1 11 - 0 Mindkét szorzóban 3 db egyes: nem

nyertünk semmit. 01111000110 1000-100010-10 100 110 -11 Van egy bonyolultabb Booth-algoritmus, amely egyidejűleg két bitet figyel, ennek sokkal hatékonyabb a kódolása. Átvitel megtakarítás - carry-save Párhuzamos: Gál, 2. kötet, 28 oldal Hogyan lehet még szorozni? (az eredeti előadás-jegyzetben a lebegőpontos osztás után van!) Van két rajzom, de csak az egyiket fogom lerajzolni, mert nagyon bonyolult az ábra és egyszerű a működés. Valamifajta párhuzamos működés van beleépítve. Hamacher: 283. oldal 1.414 Osztás A hagyományos osztás kivonásra visszavezetve C := A/B=150/48 Számoljuk közben mindig, hogy hányszor vontuk ki! 150 : 48 Eredmény: 3,1. -48 I. 102 -48 II. 54 -48 III. 60 -48 I. 28 FA1 120 -48 72 -48 24 - I. II. megvizsgálom, hogy az osztandó nagyobb-e mint az osztó, s ha igen, akkor az osztót kivonom az osztandóból. Külön gyűjtöm, hogy hányszor sikerült kivonni amennyiben már nem teljesül a feltétel, akkor a

gyűjtőből kiírom a felgyűjtött eredményt; és az osztót tizedére csökkentem (úgy, hogy az osztandót 10-zel szorzom). - Geometriai értelmezés: legfontosabb alapelv, hogy az osztandóra elkezdem elölről rámérni az osztót, s számolom, hogy hányszor fér rá, majd pedig amikor már nem fér rá, az eredményt kiírom, az osztót tizedére csökkentem, s ismét elölről rámérem, hgy hányszor fér rá. stb. Eredmény Geometriai értelmezés 0 50 100 48 48 Algebrai értelmezés 150 3, 6 0 1 2 3 4 48 5 (azosztót tizedére csökkentem) 6 6 48 4,8 6 3,1 1,2 4,8 6/48: az osztót tizedére kellett csökkentenem, hogy a 6-ra legalább egyszer ráférjen. Ugyanakkor az eredményben is megkezdem a következő helyiérték kialakítását. 6 4,8 = 60 48 Hátrány, hogy minden lépést egy komparálás előz meg, ami rendkívül időigényes. Hogyan tudnánk gyorsabban kezelni az előjel-váltást, hisz ekkor véglegesedik az eredményünk.

Visszatérés a nullán át (restoring) Ezt kivonás és előjelvizsgálattal is kiválthatjuk, s amikor az előjel negatívvá válik, akkor meghívom a következő alprogramot: kiírom a gyűjtött eredményt, a levont osztót hozzáadom, szorzom a kapott maradékot tízzel, majd visszaadom a vezérlést a főprogramnak s folytatom tovább az eljárást. 29 1,2 4,8 1,2 0,48 FA1 150 -48 102 -48 54 -48 6 -48 -42 +48 60 -48 120 -48 72 -48 24 : 48 I. Eredmény: 3,1. II. III. I. I. II. Szépen hagyjuk kivonni tovább, és ha a maradék negatívvá válik, akkor visszaállítjuk az előző (azaz az utolsó pozitív) maradékot: visszatérés a nullán át. Az algoritmus hiányossága, hogy ciklikusan fölösleges műveleteket végzünk. Visszatérés nélküli osztás (nonrestoring) Amikor elérem a negatív maradékot, nem képezek pozitív maradékot, hanem hozzáadom az osztandót (visszafele számolok): +11 -6 +5 -6 -10 +6 -4 +6 +20 -6 +14 -6 +8 -6 +20 +6 -14 +6

Eredmény: 1,83 I. 0. lépés 9. lépés 8. lépés I. II. III. 0. lépés 9. lépés Ezt kivonás és előjelvizsgálattal is kiválthatjuk, s kétféle eljárást alkalmazok: amikor az előjel negatívvá válik (negatív maradék), akkor a következőt kiírom a gyűjtött eredményt, s ezt a lépést 0.-nak tekintem a maradékot szorzom tízzel, hozzáadom az osztót, ezt a lépést 9.-nek tekintem; majd ciklikusan hozzáadom az osztót, (visszafele számolva az eredményt), amíg csak előjelváltás nem történik. amikor az előjel pozitívvá válik (pozitív maradék), akkor a következő: kiírom a gyűjtött eredményt, a maradékot szorzom tízzel; kivonom az osztót, s ezt a lépést az 1.-nek tekintem 30 FA1 majd ciklikusan kivonom az osztót, (előre számolok), amíg csak előjelváltás nem történik. visszaadom a vezérlést a főprogramnak s folytatom tovább az eljárást. stb. Geometriai értelmezés: - legfontosabb alapelv, hogy az osztandóra elkezdem

hátulról rámérni az osztót, tehát a negatív maradékot mérem, hányszor fér rá. Mivel a negatív maradékra mérem az osztó tizedét, ezért a végéről, ha egyszeri ráméréskor következik be az előjelváltás, akkor 9-tized valamennyi az eredmény, ha a második ráméréskor következik be az előjelváltás, akkor 8-tized valamennyi az eredmény stb. Geometriai értelmezés -1 0 0,6 0,6 5 0,6 9. 8 1. 10 6 Algebrai értelmezés (azosztót tizedére csökkentem) 1 10 0,6 6 Ha egyszer sem fér rá, akkor rögtön osztjuk tízzel s próbáljuk rámérni. Ha ismét nem fér fel, osszuk ismét tízzel. Egy áramkörön megvalósítható lehet a szorzás és az osztás együtt, de az bonyolult Mi van akkor, ha az A negatív szám (ha a B negatív, az mindegy). Pl pozitívvá alakítjuk s az eredmény előjelét beállítjuk. 1.415 A fixpontos multimédia feldolgozás Hang A hanghullám eredetileg analóg jellegű, ezt először digitálissá kell konvertálni annak

érdekében, hogy a számítógépen használhassuk. Ezt a technikát alkalmazzák a zenei CD-készítése során is Az analóg hullámból meghatározott időnként mintát vesznek. A minta amplitúdóját egy elektronikus áramkör méri, amit A-D konverternek, azaz analóg-digitális konverternek nevezzük. Így alakul át az analóg jel digitálissá. A felbontás és a mintavételi gyakoriság Ez egy tipikus hanghullám 31 FA1 amplitúdó +64 +32 +16 0 -16 -32 idő - az amplitúdó (x tengely) és a felbontás, azaz hány pontra bontjuk (y tengely): az analóg hullám pozitív szélső értékéhez rendelhetjük a legnagyobb ábrázolható pozitív számot, a negatív szélső értékéhez pedig a legnagyobb ábrázolható negatív számot. Digitális kód esetén az alkalmazott bitek száma határozza meg, hogy hányféle diszkrét értéket tudunk rögzíteni, azaz a felbontást. Amennyiben 8-bites kódot használunk, akkor 256-féle értéket, azaz hangszintet

rögzíthetünk. Napjainkban a jó minőségű, CD-minőséget nyújtó rendszerek sokkal finomabb felbontást biztosítanak, mivel 16-bites ábrázolást használnak. Már napirenden van a 24-bit alkalmazása az amplitúdó-ábrázolásra; a mintavétel gyakoriságát pedig úgy kell megválasztani, hogy az analóg jel minél kisebb változásait is le tudjuk képezni. Az audio jelek esetén, ha ez a leképezési gyakoriság 50 Kilohertz, ez azt jelenti, hogy másodpercenként 50 ezer mintát vesznek. Alkalmazás Mintavételi gyakoriság (KHz) 8 44,1 48 Digitális telefon Audio CD DVD Audio Codec ‘97 Professional audio recording DVD minőségi 96 A feldolgozandó adatok jellege és mennyisége - - Az amplitúdó azaz a felbontás mérésére, kvantifikálására a fixpontos (integer) adat-ábrázolást említettük. A lebegőpontos ábrázolás viszont jóval nagyobb értelmezési tartományt biztosítana. A hang- és beszédfeldolgozás során azonban igen fontos a

feldolgozási sebesség Míg az gyors integer feldolgozás viszonylag olcsón megvalósítható, a gyors lebegőpontos feldolgozásnak csupán napjainkban teremtődnek meg a hardver-feltételei (Intel Katmai processzor KNI vagy MMX2 utasítás-feldolgozása). Ez új távlatokat nyithat a hang- és beszédfeldolgozásban; A felbontás és a mintavételi sebesség határozza meg azt az adatmennyiséget, amit a digitalizálási folyamat során előállítunk és rögzítünk. Sztereo esetén ez a mennyiség megduplázódik, mivel két független információs csatornát kell majd táplálnunk. A 44,1 KHz mintavételi sebességgel dolgozó 16-bites CD audio ilyen módon minden másodpercben 150.000 bitet dolgoz fel és rögzít, ami percenként mintegy 9 megabájtot jelent (44100 x 2 bájt = 88200 bájt/sec = 88 Kbájt/sec mono esetén, sztereo esetén: 88x2 = 176 Kbájt/sec x 60 = 10 Mbájt/perc). 32 FA1 A hangok digitális feldolgozása tehát két vonatkozásban jelent mennyiségi

erőpróbát, ugyanis hatalmas mennyiségű fixpontos adatot kell tárolni, esetleg Interneten átvinni és feldolgozni. Képfeldolgozás: bittérképes vagy raszter megjelenítés Fényképeket, festményeket jellemezhetjük a színek, árnyékok, formák és a szerkezet folyamatos variációjával. Ezeket a gyakorlatban úgy digitalizálhatjuk, hogy a kép minden egyes pontjához hozzárendeljük a jellemezőit (színét, fényességét). Ezt a kép-kategóriát digitalizálhatjuk, azaz számítógéppel feldolgozható formátumra alakíthatjuk scanner-rel, digitális fényképezőgéppel vagy video-felvevővel. A felbontás és a színskála A valóságban, a valóságos képekben folyamatos a színek, a fények és árnyékok változása. A digitalizált kép pontokra bontva az eredetit, nyilvánvalóan csak közelítése lehet ennek a valóságnak. Nyilvánvaló azonban, hogy minél kisebbre vesszük ezt a pixelnek nevezett pontot, annál jobban megközelíthetjük az eredeti

képet. Tehát a kép valósághűségét a felbontás alapvetően befolyásolja A képet tehát ábrázolhatjuk a memóriában is és a képernyőn, papíron is, mint egy mátrixot azaz egy kétdimenziós tömböt, melynek minden egyes eleme egy pixel jellemzőit tartalmazza. Például az elterjedt képernyők 800x600 pixelt tartalmaznak, a mai jó felbontásúak 1280 x1024 pixelt. A színes képeket háromféle elemi színből állítjuk elő: a sárga, a kék és a bíbor, tehát minden egyes pixelhez három számértéket kellene tárolni. Ennek kiküszöbölésére a színskálát a gyakorlatban kódoljuk, s a színkódnak megfelelő színt a színfordítási táblázat segítségével értelmezhető a szín megjelenítéséről gondoskodó periféria (nyomtató, képernyő) által. 1 biten csak azt tudjuk megmondani, hogy az adott pixel világos legyen vagy sötét. 8-biten már 256 féle színkódot tudunk ábrázolni, ami még nyers színábrázolást biztosít. Ma a tipikus

alkalmazások (high color) 16-bites színskálát használnak, az úgynevezett igazi színes (true color) pedig 24 bitest. Létezik már 32-bites rendszer is, azonban ennél az alfa-csatornának nevezett 8 többletbiten már nem színeket, hanem effektust, a pixel átlátszósági mutatóját tárolják. A színek ábrázolására igényelt memória: Felbontás (pixel) 800x600 1280x1024 Memória-igény (byte) 8-bites színskála 16-bites színskála 480.000 960.000 1.310720 2.621440 Műveletek a pixeles képeken (képfeldolgozó utasítások) Tipikus műveletek a bit-blokk átvitel, a rajzolás-festés és napjainkban az ablakkezelés. Az utóbbi esetén minden megnyitott ablakot egy bit-blokként kezel a gép. Így az ablak-műveletek nem bájtonként, hanem blokkonként értelmezettek, tehát sokkal gyorsabbak. A feldolgozandó adatok jellege és mennyisége - A színskála mérésére, kvantifikálására az elmondottakból láthatóan a legalkalmasabb a fixpontos (integer)

adat-ábrázolás; A felbontás és a színskála határozza meg azt az adatmennyiséget, amit a digitalizálási folyamat során előállítunk és rögzítünk. A példában láthattuk, hogy egy 1280x1024 pixeles képernyő pillanatnyi tartalma 16-bites színskála esetén 2,5 Mbájt memória felhasználásával definiálható. Amikor műveleteket végzünk, akkor ilyen tömegű fixpontos adattal kell dolgoznunk. A raszteres képek digitális feldolgozása tehát két vonatkozásban jelent mennyiségi erőpróbát, ugyanis hatalmas mennyiségű fixpontos adatot kell tárolni, esetleg Interneten átvinni és feldolgozni. 33 FA1 A fixpontos multimédia feldolgozási irányai Adattárolás és -átvitel A digitális multimédia adatok természetesen tömöríthetők, mint bármely más adat. A tömörítést igen sokféle algoritmussal elvégezhetjük. Audio adatok estén például a Win95 Control Panel Multimédia ikon Audio részén kinyitva az Advanced menüt: széles

választékot találunk. A gyakorlatban elterjedt az MPEG (Moving Picture Expert Group) szabvány, mely a hang és a kép tömörítését egyaránt szabályozza. Hangtömörítés Bár az MPEG szabvány alapvetően videóra vonatkozik, de leírja a filmeket kísérő audio-szabványt is. Ennek 3 szintje van, minél nagyobb a szám annál komplexebb és eredményesebb a tömörítés. A szám közömbös a minőség szempontjából, hiszen mindhárom a 32, a 44 és a 49 KHz-es mintavételi sebességet engedi meg. Az MPEG szabvány nem definiálja a tömörítési algoritmust Minden MPEG állomány egy fejjel indul, mely tartalmazza a tömörítési szintet és a tömörítési módszert. Vegyük észre: a tömörítés nem igényli a real-time feldolgozást, sőt a gyakorlatban sohasem fut valós üzemmódban, míg a kicsomagolásnak a lejátszás alatt mindig valós üzemmódban kell futni. Tehát ez van inkább a sebességre kihegyezve. Képtömörítés JPEG Igen jó minőségű

képtömörítést biztosít. Jól tömörít, nem romlik a képminőség, rétegelt továbbítást biztosít: a kontúrokat gyorsan átküldhetjük vele, amit majd folyamatosan finomít. Egy sor tömörítési technika használatát engedélyezi, minden tömörítési részlet a képfile fejében található, ami elsőként kerül átküldésre. MPEG Az MPEG csak a video-képek különbségét tárolja, így ér el igen nagyfokú tömörítést. Hang vonatkozásában a sztereo-t teszi lehetővé. Az MPEG-1 1992. októberében vált nemzetközi szabvánnyá A Pentium MMX processzorok képesek real-time dekódolásukra. Az MPEG-2 jobb képfelbontást (720x480) és surround hangot biztosít. Az MPEG-3 tovább javítja a képfelbontást: 1920x1080, 30 Hz sebesség mellett. Az MPEG-4 pont ellenkező irányú, az igen alacsony átviteli sebességű alkalmazásokat célozza. Így mozgó képet lehet továbbítani 4800-64000 bit/sec mellett, azaz a hagyományos modemeken. A képfelbontás kb.

176-144 pixel, 10 Hz sebesség mellett Például videofonok vagy videokonferenciák alkalmazhatják. Adatfeldolgozás PC-környezetben A multimédia feldolgozás infrastrukturális bevezetőjét összegezve: a multimédia feldolgozás számítástechnikai szempontból hatalmas mennyiségű fixpontos és lebegőpontos adat általában valós idejű feldolgozását jelenti. Architekturálisan ezt a feladatot kétféleképpen valósíthatjuk meg: 34 FA1 - multimédia segédprocesszorral, illetve az általános célú processzorunk multimédia célú bővítésével, az MMX kiterjesztéssel. Mindkét vonal él, mindkét vonalat intenzíven fejlesztik az egész világon. Mindkettő rendelkezik a maga előnyeivel és hátrányaival. Ma még nem dőlt el, melyik a jövő útja Mi most csak az utóbbival fogunk foglalkozni. Multimédia segédprocesszorral A grafikus segédprocesszor eredeti feladata a megjelenítő rendszer gyorsítása úgy, hogy az alapfeldolgozást végző

mikroprocesszor kiegészítették egy olyan mikroprocesszorral, amit a videoorientált parancsok végrehajtására optimalizáltak. A Windows elterjedésével minden PC intenzív grafikus feldolgozást végez, ezért jelentősége megnőtt. Az általános célú processzorunk multimédia célú bővítésével, az MMX kiterjesztéssel - az MMX rövidítés a Matrix Math eXtension, vagy MultiMédia eXtensions-ként dekódolható; 1997. januárjában jelent meg a Pentium MMX processzorban A fixpontos MMX feldolgozás A pakolt adattípusok Az Intel a Pentium MMX bevezetésével sajátos 64 bit hosszúságú MMX-csoportot hozott létre, annak érdekében, hogy ezzel is segítse a 64-bites belső adatsín hatékonyabb kihasználását. Ezek fôbb jellemzôit az alábbi táblázat foglalja össze. Mértékegység Alapegység Pakolt bájt Pakolt félszó Pakolt szó bájt (8 bit) félszó (16 bit) szó (32 bit) Az alapegységek száma 8 4 2 Az Intel cég 64 bit hosszúságú MMX

adattípusai Az MMX segédprocesszor a multimédia műveletek gyors végrehajtására szolgál. Mai szemmel nézve: a grafikus gyorsítót (graphic accelerator) leemeli a video-kártyáról és beviszi a processzorba. Az MMX egy viszonylag olcsó multimédia gyorsítást eredményez. A közeljövőben úgy tűnik, hogy az MMX, az AGP és a 3D gyorsító együttese fogja biztosítani a nagyteljesítményű architektúrát. Összeadás pakolt adattípussal Feladat: adjunk össze a memóriában két raszteres képet, hogy megjelenítsük az eredőjét. Mindkét kép minden pixeljét egy bájt írja le a memóriában. Megoldás hagyományos architektúrával 1. 2. 3. 4. beolvassuk az első kép első bájtját a memóriából az akkumulátorba; összeadjuk az akkumulátorban lévő első kép első bájtját a memóriában lévő második kép első bájtjával; az eredményt kiírjuk az akkumulátorból az eredmény tárolására szolgáló memória-terület első bájtjaként;

Megismételjük az 1-3 lépést annyiszor, ahány pixelből áll a kép. Láttuk, hogy egy 800x600-as kép 960.000 pixelből áll Ez nyilvánvalóan tetemes idő Megoldás MMX architektúrával Az MMX kiterjesztés a 8 db 80 bit hosszúságú lebegőpontos regisztert használja 8 db 64 bit hosszúságú MMX regiszterként. Ezek felhasználásával a feladat megoldása a következő: 35 FA1 beolvassuk az első kép első nyolc bájtját a memóriából az MMX regiszterek egyikébe, az adatformátum pakolt bájt; beolvassuk a második kép első nyolc bájtját a memóriából egy másik MMX regiszterbe, az adatformátum pakolt bájt; elvégzünk egy pakolt bájt formátumú összeadást, ami fizikailag 8 db összeadó párhuzamos működését jelenti, melyek az eredményt az erre kijelölt MMX regiszterben képezik; az eredményt kiírjuk ebből az MMX regiszterből az eredmény tárolására szolgáló memóriaterület első nyolc bájtjaként; Megismételjük az 1-3 lépést

annyiszor, ahány pixelből áll a kép osztva nyolccal. 1. 2. 3. 4. 5. A feladatot tehát nyolcszor gyorsabban oldottuk meg. MM1 MM2 MM3 7 + 7 = 7 6 + 6 = 6 5 + 5 = 5 4 + 4 = 4 3 + 3 = 3 2 + 2 = 2 1 + 1 = 1 0 + 0 = 0 Vegyük észre, hogy ez egyetlen utasítással több adatat feldolgozását végezhetjük el, tehát ez a Single Instruction Multi Data (SIMD) feldolgozási kategóriához tartozik. Az MMX SIMD FX utasításkészlet tartalmazza a négy alapművelet és a logikai műveletek végrehajtására szolgáló utasításokat, a pakolt bájt, a pakolt félszó és a pakolt szó vonatkozásban. Az MMX kiterjesztés annyira sikeresnek bizonyult, hogy a Pentium II sorozatban már két futószalagon hajtják végre ezeket az utasításokat. 1.42 Lebegőpontos számok 1.421 A lebegőpontos ábrázolás-kialakulásának oka és formája A fixpontos számábrázolásnak két hátrányos tulajdonsága van: az ábrázolható számok értéktartománya viszonylag kicsi (két

bájton például csak -32768 . +32767), másrészt az ábrázolt számok pontossága is erősen korlátozott, hiszen ha a törtpontot a szám végére képzeljük, az egész számok közötti számtartományok a gép számára nem léteznek. Ez azzal az eredménnyel jár, hogy egyes műveletek pontaqtlanul végezhetők. (pl 7/4=1) Ezeket a hátrányokat küszöböli ki a bonyolultabb, de bizonyos tekintetben pontosabb, úgynevezett lebegőpontos számábrázolás. A lebegőpontos ábrázolás a számok hatványkitevős felírásán alapszik A szám hatványkitevős alakjának azt a felírási formát nevezzük, amelyben a számot egy egész és egy törtrészből álló szám, valamint a számrendszer alapja hatványának szorzataként írhatjuk fel, ez a matematikában tanult normál-alakhoz hasonló, bár nem abba a tartományba esik: Általánosan felírva a számot M*rk alakkal szemléltethetjük, ahol az "r" a számrendszer alapja (radix), M a szám mantisszája, k

pedig a szám karakterisztikája. A radix általában egy architektúrán belül valamennyi valós értékű szám ábrázolásánál azonos, ezért azt nem szükséges expliciten deklarálni. Így egy számhoz az ábrázolásához négy adatot kell ismernünk: a mantissza előjele (a szám előjele) a mantissza abszolút értéke a kitevő előjele a kitevő abszolút értéke. 1.422 A lebegőpontos ábrázolás története Neumann János még ellenezte a lebegőpontos számok használatát, mivel az szerinte 36 FA1 - egyrészt igen memória-pazarló, másrészt pedig növeli az aritmetikai és a vezérlőáramkörök komplexitását. A 70-es években három irány terjedt s ezek a gépek napjainkig is ezt használják: IBM 370/390: 16-bites radixt használt, így nem alkalmazhatta a rejtett bitet. A karakterisztikája 7, a mantisszája 24 bites (6 db hexadecimális szám) volt; VAX: ez hasonlított leginkább a későbbi szabványra: a 32-bites változata például

rendelkezett rejtett bittel, 8-bites volt az karakterisztika és 23-bites a mantissza. Cray-2: 15-bites karakterisztikával és 48-bites mantiszával rendelkezett. Az évek során felhalmozódó tapasztalatok alapján kezdődött meg a szabványosítási munka az IEEE keretén belül 1977-ben W. Kahan vezetésével Egyetlen korábban létező szabvánnyal sem egyezett meg, hanem inkább összeszedte nagyon sokféle architektúrából az ügyes megoldásokat. Bár a szabványt csak 1985-ben hagyták jóvá, az első implementációja már 1981-ben megjelent. Ez volt az Intel 8087-es matematikai segédprocesszor. 1.423 A lebegőpontos ábrázolás jellemzői Radix Annak érdekében, hogy a művelet kiszámítható legyen, kívánatos, hogy a hatványra emelendő radix egyezzen meg a mantisszánál használt számrendszer alapjával. A legtöbb számítógép architektúránál ez 2. Az IBM 370 radixa 16, hatékonyság-növelési célokból Ennek eredményeképpen normalizáláskor

4bitenként kell elshiftelni, s a normalizálás is csak akkor szükséges, amennyiben a legmagasabb helyiértékű négy vagy több bit nulla. Az értelmezési tartomány A karakterisztika helyiértékeinek száma 1 A tízes számrendszerben ábrázolható számtartomány 2 3 4 Kettes számrendszer maximális érték ±9 1=1 ±9 ±99 11 = 3 ±9 ±9 ±999 ±9 ±999 az ábrázolható számtartomány ±2 ±1=±2 ±2 ±3=±8 111 = 7 ±2 ±7=±128 1111 = 15 ±2 ±15=±32.768 a két nyíl a növekedési irányt jelzi Tehát az ábrázolt értelmezési tartomány függ: a karakterisztika számára rendelkezésre álló bitek számától valamint a radixtól. Pontosság Létezik még egy számhalmaz, ami nem ábrázolható, mivel az ábrázolható számok között helyezkednek el. Például, amennyiben a mantissza mindössze három jegyű, akkor a 0,3114x10+6 már nem ábrázolható és kénytelenek vagyunk közelíteni a 0,311x10+6 értékkel, tehát 400-at elveszítettünk. S ha ez

a mi saját angol fontunk, az már egy komoly summa.A pontosság tehát a mantissza bitjeinek számától függ. A normalizált jellemző A lebegőpontos ábrázolásmódnak a hátránya, hogy ugyanannak a számnak nincs egy unikális ábrázolási módja. például a 37,135 felírható mint 0,037135 x 103 vagy 3713,5 x 10-2 . Ezeket hívjuk nem normalizált számoknak. A normalizált számok viszont azt igénylik, hogy a lebegőpontos szám tizedes vesszője legyen egy meghatározott pozíción, például a legnagyobb helyiértékű számtól álljon balra. Ebben az esetben teljesül a következő egyenlőtlenség: 37 FA1 1/r ≤ M 1 Fontos észrevenni, hogy a mantissza értéke nem érheti el az egyet, tehát feltétlenül kisebb egynél. Például ez a két általunk használt számrendszer esetén: 1/10 ≤ M 1 1/2 ≤ M 1 Az ilyen normálalakban történő számábrázolásnak két csoportja van: binárisra normált és hexadecimálisra normált alak. Meg

kell jegyezni, hogy a normalizált ábrázolási mód nem teszi lehetővé néhány, a nullához közeli szám ábrázolását. -0,1x10-n -0,999999x10+n-1 túlcsordulási régió az érvényes számok tartománya 0 +0,1x10-n alulcsordulási régió +0,999999x10+n-1 az érvényes számok tartománya túlcsordulási régió Miért n-1 a pozitív kitevő? A karakterisztika maximális értéke fenn vann tartva a végtelen jelzésére. Ez a mantissza előjelével kiegészülve jelenti a pozitív illetve a negatív végtelent. Alulcsordulás, túlcsordulás A fenti ábrán látható, hogy létezik a legnagyobb ábrázolható érték és természetesen a legkisebb is. Ezt hívjuk túlcsordulásnak és a kis számok esetén pedig alulcsordulásnak. Az architektúrának biztosítania kell ezek bekövetkezésének felfedezését, kezelését és jelzését. Túlcsordulás esetén az IEEE lebegőpontos szabvány esetén a gép kijelzi és egyidejűleg vagy beállítja a legmagasabb

létező értéket, azaz előjeles végtelent ábrázol. Az IEEE lebegőpontos szabvány esetén például az alulcsordulást kell tudni kijelezni és az értékét nullára konvertálja vagy a denormalizált számot ábrázolja. Denormalizált számok Tehát mit is jelent a denormalizált szám? 0 0,1 0,2 alegkisebbábrázolhatónormalizált száma0,1x10 -n -nenormalizált szám a0,04x10 d A lebegőpontos számok írásakor általában az E betűvel szokták elválasztani a mantisszát a karakterisztikától. A 02E-n és a 01E-n normalizált számok, melyek kielégítik a fenti egyenlőtlenséget A 0.04E-n már kisebb, mint a legkisebb normalizált szám, ezt denormalizáltnak hívjuk Abban az esetben, ha a denormalizált számok esetében megengedjük, hogy ne kelljen kielégíteniük a fenti 38 FA1 egyenlőtlenséget, azok rögtön ábrázolhatóakká válnak. Erre képes például az IEEE lebegőpontos szabvány. A nulla ábrázolása A nulla környékét vizsgáljuk. A

pontosan nulla szám ábrázolása a lebegőpontos formátumnál problémákat okozhat. Azt mondhatjuk, hogy minden olyan ábrázolás, melynél a mantissza csak nullából áll, interpretálható nullaként, úgy, hogy bármi is legyen a karakterisztika értéke. Ugyanakkor kívánatos, hogy az exponens mező legyen egyenlő szintén nullával. A rejtett bit Ennek az ötlete öregebb, mint az elektronikus számítógép. Konrad Zuse az 1936-ban épített relés gépében már alkalmazta. Bináris normálás esetén - a nulla értéket kivéve - a mantisszára korábban felírt egyenlőtlenség csak akkor teljesülhet, ha a kettedes pont utáni első helyértéken 1 áll (a szám csak így lehet nagyobb vagy egyenlő 0,5-nél). Mivel ez mindig egyes, így nem hordoz semmiféle információt, ezért nincs szükség arra, hogy tároljuk. Ez lehetővé teszi, hogy a mantissza hossza egy bittel növekedjen Csupán amikor a lebegőpontos számot használják (a számításokban), akkor kell

az 1-nek jelen lenni, amikor pedig tárolják, ismét eltűnik. Ezt a bitet hívják rejtett bitnek A rejtett bit technikát sok architektúra használja, a lebegőpontos processzorok belső adatábrázolásában pedig magukban kell foglalni a rejtett bit kezelését. Az őrző bitek (guard bits) Kívánatos, hogy a művelet eredménye a lehető legpontosabb legyen. Ezért fontos, hogy a relatív hiba kisebb legyen, mint a normalizált eredmény legkisebb számjegye. Ebből a célból őrző biteket vezettek be, melyek a mantissza legkisebb helyiértéke után találhatók. A céljuk, hogy megőrizzék azokat a számjegyeket, amelyeket később, a normalizálás során balra shiftelünk illetve kerekítésnél tudjuk őket használni. Az őrző bitek gyakorlati megvalósítása: a lebegőpontos műveletek végrehajtása céljából az operandusokat az ALU regisztereibe töltjük. Ezek a mantissza vonatkozásában mindig hosszabbak, mint a tárolt mantissza+amennyiben van, a rejtett

bit. Értelemszerűen az eredmény is mindig egy hosszabb regiszterben keletkezik. Ezt pedig tárolás előtt mindig kerekíteni kell, egyrészt hogy beférjen a kisebb tárolóhelyre, másrészt pedig a számolási pontosság növelése céljából. A karakterisztika (exponens) ábrázolása A karakterisztikát következő megfontolásokból feszített előjeles vagy többletes kódban ábrázolják: egyszerűbb, mint a komplemens kód; a többletes kód megfelelő a karakterisztika műveletekhez, mivel azokat csak összeadni-kivonni kell tudni. Például a szám kitevőjét hozzáadjuk az 10000000 bináris konstanshoz, és az összeget tároljuk 8 biten. A kitevőnek ilyenformán történő tárolását feszített előjeles vagy 128-többletes tárolásnak nevezzük, mivel 128-at adunk hozzá a kitevőhöz (additív kód). A pozitív kitevő tehát hozzáadódik a 128-hoz, a negatív kitevő pedig levonódik belőle. Így a kitevő ábrázolási tartománya -128 és +127 közé esik

Ez megegyezik tehát egy 8-bites kettes komplemens ábrázolási formával, úgy, hogy 128-at hozzáadtunk, vagy egy 8-bites kettes komplemens ábrázolási formával, úgy, hogy az előjelbitet invertáltuk. Régi nagy gépeknél a karakterisztika 7 bit hosszúságú volt, itt értelemszerűen 64-többletes ábrázolást használtak; az Intel 80387 esetén dupla pontosságú számok esetén 1023, bővített pontosságú számoknál pedig 16.383-többletes kódot használnak Az exponens kódképe: 39 FA1 0- mínusz 1- plusz -128 0 +127 1.424 Az IEEE 754 lebegőpontos szabvány A szabvány kidolgozásának célja, hogy megkönnyítse a különféle processzorú számítógépek közötti program-portabilitást s egyben bátorítsa a magas-színvonalú numerikus szoftverek kidolgozását. A szabvány rendszer-szintű megvalósításban gondolkodik. Tehát a hardver és a szoftver együttesen biztosítja a szabványnak megfelelő működést. Azaz semmi problémát nem jelent,

ha a hardver nem felel meg tökéletesen a szabványnak, s teljességgel korrekt az a megoldás, amikor az igen ritkán előforduló eseteket a szoftver kezeli le. A jelenleg elterjedt Intel és Motorola processzor-család ezen szabványt alkalmazza. Ettől eltérő formátumot használ például az IBM 390 és a VAX család De már megjelentek olyan IBM és VAX processzorok, melyek az IEEE 754-es lebegőpontos szabványt használják. A szabvány lebegőpontos ábrázolás négy aspektusát tárgyalja: az adattípus formátumát; a műveleteket a kerekítést és a kivételek kezelését. A lebegőpontos formátumok A számítógépes rendszerek gyakran kezelnek több valós formátumot, mivel egyrészt a memóriával való takarékosság tömör formátumot igényel; másrészt pedig egyetlen tömör formátum túlságosan korlátozott az igényelt pontossághoz és értéktartományhoz. Ezen megfontolások alapján az IEEE lebegőpontos szabvány is több formátumot deklarál.

Ezeket két csoportba soroljuk: szabványos (egyszeres és kétszeres pontosságú ábrázolás) és kiterjesztett. A megvalósításnak minimum az egyszeres pontosságú formátumot kell biztosítania, hogy kielégítse a szabványt. A kétszeres pontosságú formátum megvalósítása már opcionális Szabványos formátum Egyszeres pontosságú (Short real vagy single precision) Hossza: 4 bájt (32 bit), ebből a mantissza 23, a karakterisztika pedig 8. 128-többletes az exponens értéke. A mantisszához tartozik a nem ábrázolt, de benne foglalt egyes, azaz a rejtett bit Értelmezési ± tartománya: kb. 10 38 (8,43*10-37 ≤ x ≤ 3,371038), pontossága: 6-7 decimális szjegy. 31 32 23 22 EXP mantisszaelõjele 0 8bit MANT 23bit kettedespont 40 FA1 Kétszeres pontosságú (Long real - double precision) Hossza: 8 bájt (64 bit), ebből a mantissza 52, a karakterisztika pedig 11. 1023-többletes az exponens értéke. A mantisszához tartozik a nem ábrázolt, de benne

foglalt egyes Értelmezési tartománya: kb 10 308 (4,19*10-307 ≤ x ≤ 1,6710308), pontossága: 15-16 decimális szjegy. 1 11 52 EXP 63 MANT 5251 0 Kiterjesztett (extended) formátum A szabvány mindkét formátumra tartalmaz egy kiterjesztett (extended) formátumot. Ezek célja, hogy biztosítson egy fokozott pontosságot és egy nagyobb karakterisztika tartományt a számítási sorozat során a közbenső eredmények számára. Például két számvektor pontos szorzatát úgy kaphatjuk meg, hogy a szorzatok összegét kiterjesztett pontossággal számítjuk ki. Maguk a számok szabványos pontosságúak (egyszeres vagy kétszeres) és az eredményt is az inputnak megfelelő pontosságúra kerekítjük vagy vágjuk. A kiterjesztett formátumok használata mérsékli a kerekítések által okozott hiba halmozódását. Az elemi függvények (sin, cos, stb) számítása során is kiterjesztett pontosság alkalmazásával mérséklik a kerekítés okozta hibát. Mivel

a kiterjesztett formátum csak a processzoron belüli számításra szolgál és nem kerül tárolásra, ezért a szabvány jóval nagyobb szabadságfokot biztosít a processzor-gyártók számára, mint a szabványos formátum estében. (Stallings 293) Bővített (extended) egyszeres pontosságú Hossza: minimum 43 bit, ebből a mantissza minimum 31, a karakterisztika pedig minimum 11. A karakterisztika értéke nem lehet nagyobb, mint a szabványos, kétszeres pontosságú ábrázolás esetén (azaz maximum 1023). Csak belső ábrázolásra használjuk Bővített (extended) kétszeres pontosságú Hossza: minimum 79 bit, ebből a mantissza minimum 63, a karakterisztika pedig minimum 15. Az karakterisztika értéke nem lehet nagyobb, mint 16.383 Csak belső ábrázolásra használjuk A bővített pontosságú egy konkrét megvalósítása (a másik az Intelen belül van leírva): A quadnak is nevezett bővített formátum hossza: 16 bájt (128 bit), ebből a mantissza 112, a

karakterisztika pedig 15 bit. 16383-többletes az exponens értéke A mantisszához tartozik a nem ábrázolt, de benne foglalt egyes. Értéktartománya: 3,4*10-4932 ≤ x ≤ 1,2104932. Csak belső ábrázolásra használjuk. Műveletek A szabvány szerint a négy alapműveleten kívül meg kell valósítani a maradék-képzőt, a négyzetgyökvonást valamint a bináris-decimális konvertálót. A pontosságnak az LSB pozíción lévő bit értékének a felénél kisebbnek kell lenni. Ez azt jelenti, hogy legalább három őrző bitet kell alkalmazni Minden formátum esetén a maximum exponens (255, 2047 és a 32767) jelenti az előjeles végtelent. Az előjeles végtelennel végzett műveleteknek is nyilvánvaló eredményei vannak. Például: 3+(+∞) = +∞ 3+(−∞) = −∞ stb. (Stallings 302) A kerekítés 41 FA1 Bármely lebegőpontos művelet eredményének mantiszája egy hosszabb ALU-regiszterben keletkezik. Ezt amikor a memóriába töltjük (store) akkor

kerekítenünk kell. Az IEEE szabvány szerint a kerekítéseknek négy alternatív megközelítése van: - - a legközelebbire való kerekítés: az eredményt a legközelebbi ábrázolható számra kerekíti. Például, amennyiben az őrző bitek értéke 101, akkor az nagyobb, mint az LSB bit értékének a fele. Ekkor tehát az LSB-hez hozzá kell adni 1-et; kerekítés a pozitív végtelen felé; kerekítés a negatív végtelen felé; az utóbbi kettő alapgondolata, az úgynevezett intervallum aritmetikában gyökerezik. A probléma az, hogy a lebegőpontos műveletsorozat végén a hardver-korlátok okozta kerekítések miatt nem ismerhetjük a pontos eredményt. Amennyiben viszont minden műveletet kétszer hajtunk végre, egyszer fölfele, egyszer pedig lefele kerekítve, akkor két eredményt kapunk, s biztos, hogy a kettő között helyezkedik el a helyes eredmény. Ha a két eredmény közötti különbség csekély, akkor elég pontos az eredményünk Amennyiben viszont

nagy, ez egy információ számunkra és szükség esetén elvégezhetünk egy kiegészítő elemzést. kerekítés a pozitív végtelen felé: kerekítés a negatív végtelen felé: -∞ - +∞ 0 a nullára kerekítés, ami gyakorlatilag az őrző bitek egyszerű levágását (trunc) jelenti, azaz ignorálását jelenti. Ez azt eredményezi, hogy a mantissza a pontos értéknél mindig kisebb vagy azzal egyenlő lesz. -∞ +∞ 0 A kerekítési technikák közül az első az alapértelmezés. Példa a kerekítési technikákra: -∞ -8,47 Az eredeti szám +8,42 -8,47 +∞ 0 a legközelebbire való kerekítés +8,4 -8,5 +8,42 kerekítés a pozitív végtelen felé +8,5 -8,5 kerekítés a negatív végtelen felé +8,4 -8,4 nullára kerekítés +8,4 -8,4 A kivételek kezelése: A kivételek felbukkanása szoftver-megszakítást eredményez, melynek kezelését a felhasználó végzi: - nem egyértelmű művelet: például egy negatív szám negyzetgyökvonása;

nullával való osztás: amikor az osztandó egy véges nemm null szám, az osztó pedig nulla, akkor az eredmény pozitív végtelen; alulcsordulás: lásd korábban; túlcsordulás: lásd korábban; nem exakt kivétel: amikor egy művelet kerekített eredménye nem exakt, ez a kerekítési szabályokból eredő üzenet. 42 FA1 1.425 Műveletek lebegőpontos számokkal A numerikus adatok tárolásának tárgyalásakor világossá vált a lebegőpontos adatábrázolási forma előnye a számításigényes feladatok megoldásánál. Ezért az alapműveletek legegyszerűbb megvalósítási formáit ebben az esetben is megnézzük. A=±mA rkA B=±mB rkB A és B a két lebegőpontos számunk, ahol mA és mB a normalizált mantisszát és kA és kB a karakterisztikát jelöli. Az r pedig a radix, a számrendszer alapja Összeadás-kivonás A lebegőpontos számok összeadása és kivonása a fixpontos számokéhoz hasonló, csak összetettebb, mivel a hatványkitevős forma miatt a

karakterisztikákat először azonos értékre kell hozni. Például össze kell adnunk a két következő számot: Operandusok Az operandusok értéke 0,3 * 103 900 * 100 A B Az őrző helyiérték Először is azonos kitevőjű alakra hozzuk őket, azaz a kisebb karakterisztikájú számot léptetjük jobbra: 900 x 100 90 x 101 9 x 102 0,9 x 103 Amikor a karakterisztikák már azonosak, elvégezzük az összeadást. 0,3x103 0,9 x 103 1,2 x 103 Végül, ha szükséges, mint az adott esetben is, az eredményt normalizáljuk. 0,12 x 104 Az algoritmus a következő: - a karakterisztikák összehasonlítása; a kisebb karakterisztikájú szám shiftelése jobbra s növeljük a karakterisztikát; ezt ciklikusan ismételjük addig, amíg a két karakterisztika meg nem egyezik; amikor azonosak a karakterisztikák, elvégezhetjük az összeadást (kivonást); végül, ha szükséges, a mantisszát normalizáljuk jobbra-balra shiftelve. Szorzás C= AxB C=±mA mB rkA+kB A mantisszát