Comments

No comments yet. You can be the first!

Content extract

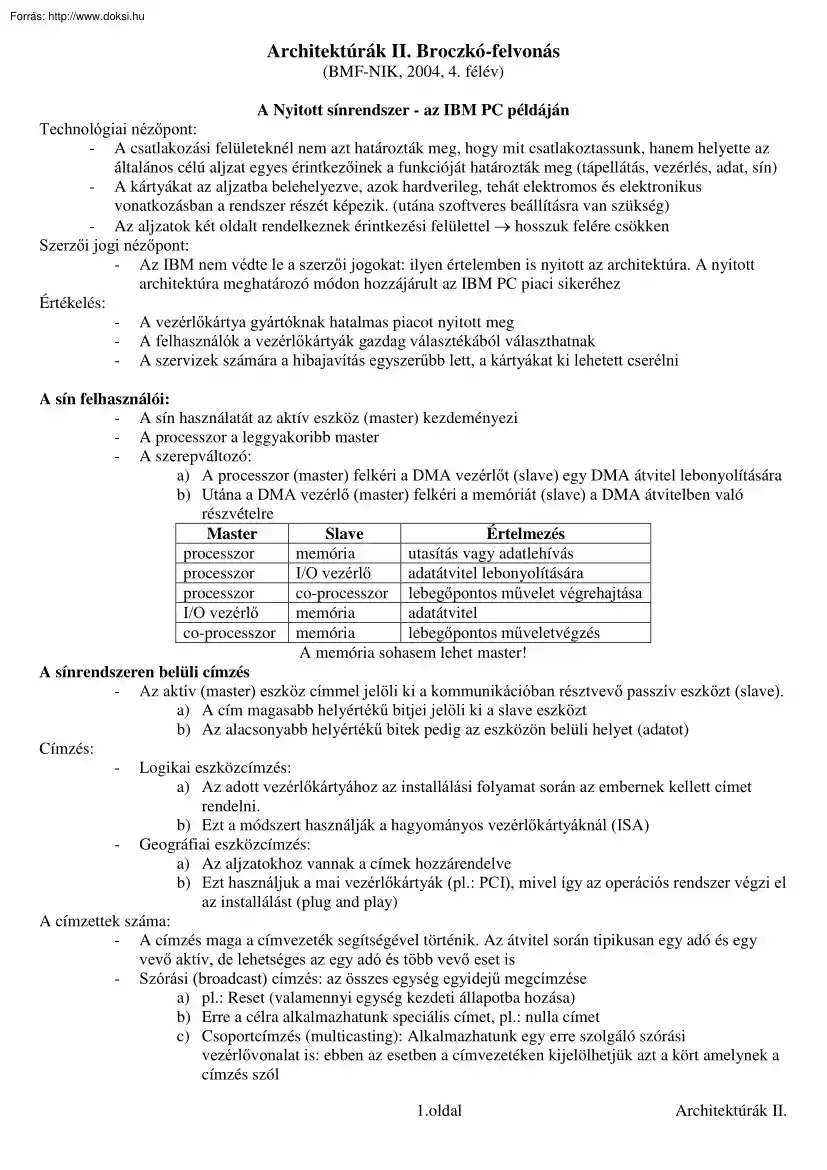

Architektúrák II. Broczkó-felvonás (BMF-NIK, 2004, 4. félév) A Nyitott sínrendszer - az IBM PC példáján Technológiai nézőpont: - A csatlakozási felületeknél nem azt határozták meg, hogy mit csatlakoztassunk, hanem helyette az általános célú aljzat egyes érintkezőinek a funkcióját határozták meg (tápellátás, vezérlés, adat, sín) - A kártyákat az aljzatba belehelyezve, azok hardverileg, tehát elektromos és elektronikus vonatkozásban a rendszer részét képezik. (utána szoftveres beállításra van szükség) - Az aljzatok két oldalt rendelkeznek érintkezési felülettel hosszuk felére csökken Szerzői jogi nézőpont: - Az IBM nem védte le a szerzői jogokat: ilyen értelemben is nyitott az architektúra. A nyitott architektúra meghatározó módon hozzájárult az IBM PC piaci sikeréhez Értékelés: - A vezérlőkártya gyártóknak hatalmas piacot nyitott meg - A felhasználók a vezérlőkártyák gazdag választékából

választhatnak - A szervizek számára a hibajavítás egyszerűbb lett, a kártyákat ki lehetett cserélni A sín felhasználói: - A sín használatát az aktív eszköz (master) kezdeményezi - A processzor a leggyakoribb master - A szerepváltozó: a) A processzor (master) felkéri a DMA vezérlőt (slave) egy DMA átvitel lebonyolítására b) Utána a DMA vezérlő (master) felkéri a memóriát (slave) a DMA átvitelben való részvételre Master Slave Értelmezés processzor memória utasítás vagy adatlehívás processzor I/O vezérlő adatátvitel lebonyolítására processzor co-processzor lebegőpontos művelet végrehajtása I/O vezérlő memória adatátvitel co-processzor memória lebegőpontos műveletvégzés A memória sohasem lehet master! A sínrendszeren belüli címzés - Az aktív (master) eszköz címmel jelöli ki a kommunikációban résztvevő passzív eszközt (slave). a) A cím magasabb helyértékű bitjei jelöli ki a slave eszközt b) Az alacsonyabb

helyértékű bitek pedig az eszközön belüli helyet (adatot) Címzés: - Logikai eszközcímzés: a) Az adott vezérlőkártyához az installálási folyamat során az embernek kellett címet rendelni. b) Ezt a módszert használják a hagyományos vezérlőkártyáknál (ISA) - Geográfiai eszközcímzés: a) Az aljzatokhoz vannak a címek hozzárendelve b) Ezt használjuk a mai vezérlőkártyák (pl.: PCI), mivel így az operációs rendszer végzi el az installálást (plug and play) A címzettek száma: - A címzés maga a címvezeték segítségével történik. Az átvitel során tipikusan egy adó és egy vevő aktív, de lehetséges az egy adó és több vevő eset is - Szórási (broadcast) címzés: az összes egység egyidejű megcímzése a) pl.: Reset (valamennyi egység kezdeti állapotba hozása) b) Erre a célra alkalmazhatunk speciális címet, pl.: nulla címet c) Csoportcímzés (multicasting): Alkalmazhatunk egy erre szolgáló szórási vezérlővonalat is:

ebben az esetben a címvezetéken kijelölhetjük azt a kört amelynek a címzés szól 1.oldal Architektúrák II. A sínrendszer működése Megosztott sínrendszer esetén két fázisból áll: - A sínfoglalás (bus arbitration) – ha két vagy több egység szeretne master lenni, akkor sínütemezésre van szükség, hogy a káoszt elkerüljük - A sínhasználat (bus timing) – maga az adatátvitel folyamata A sínfoglalás Soros sínfoglalás: - Hardver lekérdezéses (daisy chain – gyermekláncfű). Előnyei: a) Kevés vezetéket igényel (olcsó) b) Elvben végtelen számú egységet tudunk csatlakoztatni Hátrányai: c) A prioritás hardveres úton szabályozott (merev) d) Az előrébb álló egységek elnyomhatják a hátrébb állókat e) Érzékeny a bus grant vonal meghibásodására Működése: Amikor az ütemező egy sínkérést észlel, használati engedélyt ad ki oly módon, hogy beállítja a sínhasználat engedélyezése jelet. Ez sorban keresztülfut

az összes egységen Amikor az ütemezőhöz fizikailag legközelebbi eszköz meglátja az engedélyezést, ellenőrzi, hogy ő adta-e ki a kérést. Ha igen, akkor átveszi a sínt, és nem továbbítja az engedélyt a következő eszköznek. Az egységek távolsága egyben a prioritásukat is meghatározza. - Szoftver lekérdezéses (software polling). Előnyei: a) A prioritás szoftveres úton szabályozott (rugalmas) b) Kevésbé érzékeny a bus grant vonal meghibásodására Hátrányai: c) több vezérlővonal (drága) d) A csatlakoztatható egységek számát a bus grant vonalak száma korlátozza, példánkban maximum 23=8 db 2.oldal Architektúrák II. Párhuzamos sínfoglaltság: a) Előnye: gyors b) Hátránya: még több vezérlővonalat igényel (még drágább), pl.: PCI Rejtett sínfoglalás: - Előfeltétele: két, egymástól független hardver vezérelje a sínfoglalást és az adatátvitelt - Amíg az aktuális adatátvitel folyik, az alatt lehetőség van

az adatsín következő használójának kiválasztására Az adatátvitel (bus timing) Szinkron adatátvitel - Fogalma: Az adatátvitel mind az adó, mind a vevő számára előre ismert időintervallumban történik - Óra-ütemadó: a) Mind az adó, mind a vevő közös forrásból kapja az órajelet (akkor alkalmazzák, ha kicsi a távolság az adó, és a vevő között) b) Mind az adónak, mind a vevőnek saját, de azonos frekvenciával járó óra-ütemadója van. Ezek időben elcsúszhatnak egymástól, ezért egy szinkronjel segítségével hangolják össze a működésüket Értékelése: - Előnye: olcsó, egyszerű a megvalósítása - Hátrány: Az előre ismert idő intervallum hosszát mindig a leglassúbb egység határozza meg ez visszafogja a gyors egységeket (ez kiküszöbölhető többszintű sínrendszer alkalmazásával, ahol átviteli-sebesség függő tartományonként csoportosítják az egységeket) A Bővítősínek fajtái: - Átviteli sebesség szerint

(szinkron meghajtású sínek): a) Kompatibilitási vagy hagyományos sín (~ 5MB/s) b) Helyi sín, pl.: PCI (lehet 132 vagy 264 MB/s) c) AGP 1x (500 MB/s) - Tervezési szempontok szerint: a) Platformfüggő, pl.: ISA, EISA b) Platformfüggetlen, pl.: USB, SCSI, PCI Aszinkron adatátvitel Fogalma: Az előző elemi művelet befejeződése egyben jelzés a következő elemi művelet kezdetére. Fajtái: - Egyvezetékes (egy vezérlővezeték) a) Adó oldali vezérlés: Először az adat az adatsínre kerül, majd késleltetést alkalmazunk. Hátránya: Az adónak nincs visszacsatolása arról, hogy a vevő valóban elolvasta-e az adatsínre helyezett adatot. Lehet, hogy a vevő ki van kapcsolva (Jobbra az alsó ábrán: Data; Data ready) 3.oldal Architektúrák II. - b) Vevő oldali vezérlés: Ez biztonságosabb átvitelt jelent, mert a vevő az átvitel igénylésének pillanatában aktív, de továbbra sincs visszacsatolás az adat célba érkezéséről. (Jobbra az alsó

ábrán: Data; Data request) Kétvezetékes átvitel (handshaking - kézfogás) a) Adó oldali vezérlés: az alsó ábrán Data, Data Ready, Data Acknowledge b) Vevő oldali vezérlés: az alsó ábrán Data, Data Request, Data Ready Az I/O rendszer Fogalma: a processzor-memória együttest a külvilággal összekapcsoló rendszer. Értelmezése: Fejlődése: - A processzor közvetlenül irányította a perifériákat Elkülönült I/O modul vezérli a perifériákat: lekérdezéses I/O (wait for flag) Elkülönült I/O modul vezérli a perifériákat: megszakításos I/O A DMA megjelenése – önállóan végzi az átvitel vezérlését Csatorna: I/O célú utasításokat dolgoz fel, közben a központi operatív tárat használja I/O processzor: I/O célú utasításokat dolgoz fel, saját operatív tárral (memóriával) rendelkezik. - A processzor közreműködésével (programozott I/O): a) Címtér: 1. Különálló I/O címtér 2. Memóriába leképezett I/O címtér b)

Működés: 1. Feltételes 2. Feltétlen Processzor közreműködése nélkül: a) DMA b) Csatorna c) I/O processzor Rendszer: - 4.oldal Architektúrák II. Programozott I/O Fogalma: minden egyes I/O művelethez a processzornak egy-egy utasítást kell végrehajtania Fajtái címtér szerint: Különálló I/O címtér. - Elve: A processzor két különálló címteret lát. - - Jellemzői: a) A címsín szolgál: 1. az operatív tár, 2. és az I/O egység címzésére b) Létezik olyan vezérlővonal (memória / I/O) mely megmutatja, hogy az adott időpillanatban a címsínen memória vagy I/O cím található c) mivel két különálló címtérről van szó, ugyanaz a cím szerepelhet memóriacímként és I/O címként is. d) Pl.: Intel esetében az eszköz 16 biten címezhető meg (65536 féle I/O cím) e) azon regisztereket, amelyeken keresztül a processzor a perifériákkal kommunikálhat, I/O portnak nevezzük, amely fizikailag a vezérlőkártyán helyezkedik el

Az I/O Port regiszterei: a) Parancs (command) regiszter, amelybe a processzor írhatja a kívánságait a perifériákhoz b) Adat (data) regiszter 1. Data input regiszter: ebből olvassa a processzor a perifériától kapott adatokat 2. Data output regiszter: ebbe írja a processzor a periféria számára küldött adatokat c) Állapot (Status) regiszter: innen olvassa a processzor a periféria üzeneteit d) Az input, output regisztereket a mai gyakorlatban összevonják: parancs állapot regiszter, adat input-output regiszter. e) Napjainkban az I/O porton belül több regiszter is található, pl.: 1. I/O egység működőképességét jelző regiszter 2. I/O egység típusát, konfigurációs jellemzőit tároló regiszter (plug & play) 3. a nagyobb teljesítményű, összetettebb I/O egységeknél több parancs-, adat-, és állapotregiszter lehetséges A különálló I/O címtér megvalósítása: - Következmény: a) Különálló utasítások szolgálnak a

memória-műveletekre (pl.: load/store), és b) Különálló utasítások szolgálnak az I/O műveletekre. Pl: Intel esetében 1. inX: a processzor olvassa be az X című I/O port adatregiszterét az AC-ba outX: a processzor beírja az AC tartalmát az X című I/O port adatregiszterébe 5.oldal Architektúrák II. - Értékelés: a) Előnyei: egyszerű, olcsó a megvalósítása b) Hátránya: a processzor részt vesz az I/O műveletekben szűk keresztmetszet c) az AC szűk keresztmetszetet jelent nagy tömegű I/O számára d) Pl.: Hálókártya (ISA), amely az IBM PC-nél különálló IO címtérrel rendelkezik e) Minden mai piacon lévő processzorban megtalálható A Memóriára leképzett I/O (Memory mapped I/O) Elve: Ezt látja a processzor Processzor Ezt az I/O egység látja Jellemzői: - A megosztás: a processzor memóriakezelő utasítással (load-store) éri el azt a közös memóriaterületet, amit a periféria is kezelhet Ebben az esetben az I/O egység

használhatja a rendszersínt nagyobb az átviteli sebesség Megvalósítása: Értékelése: - Jóval gyorsabb, mint a különálló I/O címtér (előny) Minden I/O esetén a processzornak egy utasítást végre kell hajtania (hátrány) Pl.: Az IBM PC-nél a képernyőkezelés Működése: Feltétlen átvitel: - A vevő mindig vételre kész állapotban van - Nem ellenőrizzük az átvitel sikerességét - Nincs szinkronizálás a vevő és az adó között. - Pl.: LED Feltételes átvitel: - Lekérdezés (wait for flag) a) A processzor beírja a kívánságát az I/O port parancsregiszterébe b) A processzor kiolvassa az I/O egység állapotregiszterének tartalmát c) Amennyiben nem „ready”, akkor vissza a (b) pontra d) Amennyiben „ready”, akkor kiolvassa az I/O egység adott adatregiszterének tartalmát, majd beírja azt az akkumulátorba (AC) Értékelése: A processzor - I/O egység közti sebességkülönbség miatt a processzor akár több milliószor olvassa be

feleslegesen az állapotregiszter tartalmát - Megszakításos: a) A processzor beírja a kívánságát az I/O egység parancsregiszterébe, majd elkezd mást csinálni 6.oldal Architektúrák II. b) Amikor az I/O egység begyűjtötte a perifériától a szükséges adatot az adatregiszterben: 1. Beállítja az állapot regiszter „ready” bitjét, és 2. Megszakításkérést küld a processzor felé c) A processzor a következő utasítás-töréspontban elkezdheti a megszakításkérés feldolgozását 1. Beolvassa az I/O egység állapotregiszterét 2. ha ott a „ready” bit be van állítva, akkor egy ennek megfelelő megszakításfeldolgozó programot indít el; ez kiolvassa az I/O port adatregiszterét és tartalmát átviszi az AC-ba DMA – Direct Memory Access Fogalma: nagy tömegű adat gyors periféria alkalmazásával történő átvitele, a processzor közreműködése nélkül Elve: Megvalósítása: DC – decrementer I/O AR – I/O Address Register I/O DR

– I/O Data Register Működése: - a DMA vezérlő „felprogramozása”: programozott I/O-val átvisszük a processzorból a DMA vezérlőbe az átvitelt leíró alapinformációkat: a) A DC-be beírjuk az átviendő adategységek számát b) Az I/O AR-be beírjuk az átviendő memóriablokk kezdőcímét c) Az adatátviteli egysége (byte, félszó, szó) d) Az átvitel irányát e) A résztvevő periféria címét, és a DMA vezérlő címét f) Az átvitel módját blokkos vagy cikluslopásos módon 7.oldal Architektúrák II. - Blokkos vagy (burst) üzemmód (pl.: Winchester esetén memóriacím-inkrementálás) a) Mihelyt a DMA vezérlő előkészítette az első átviendő adatelemet az I/O DR-ben, akkor egy DMA request jelzést küld a processzornak. Ezzel kéri a rendszersín használati jogát! b) A processzor DMA acknowledge jelzéssel lemond a rendszersín használati jogáról c) A DMA vezérlő beírja az I/O DR tartalmát az I/O AR által kijelölt

memóriacímre, majd a DC értékét csökkenti, az I/O AR értékét növeli d) Ez a ciklus addig fut, míg a DC értéke nullára nem csökken - Cikluslopásos (cycle stealing) átvitel Értékelése: Míg az utasítás-töréspontban a megszakítás feldolgozással a processzorra további munka várhat, addig a DMA töréspontban a DMA vezérlő a processzor helyet dolgozhat. Csatorna - A DMA koncepciójának kiterjesztése a lassúbb perifériákra A processzor és a csatorna közös operatív tárat használ. A memóriában lévő I/O utasításokat a csatorna, nem pedig a processzor hajtja végre. Továbbra is vannak I/O egységek, azonban ezek munkáját a csatorna fogja össze, a processzor helyett. Fajtái: - - Szelektor csatorna a) a gyorsabb egységeket fogja össze b) Közülük mindig csak egy kommunikálhat egyszerre c) Megvalósítása: ábra Multiplex csatorna: a) A lassúbb egységeket fogja össze b) Közülük több kommunikálhat egyszerre c)

Megvalósítása: ábra d) Fajtái: 1. Bájt multiplexer: az átvitel során a legnagyobb sebesség elérése a cél Pl.: 3 egység kommunikációja esetén: Aegység=A1, A2, A3, A4, Begység= B1, B2, B3, B4, Karakter sorozata Cegység= C1, C2, C3, C4, Eredő adatfolyam: A1 B1 C1 A2 C2 A3 B2 C3 A4 C4 A5 B3 C5. 2. Blokk multiplexer: a byte multiplexerhez hasonlóan blokkszinten végzi a munkáját. Pl: IBM 360-as gépcsalád 8.oldal Architektúrák II. Egy hipotetikus számítógép tervezése Korlátaink – jellemzők: - minden utasítás két byte hosszú (256 lehetséges cím): MK címrész 1 byte 1 byte - két egységből áll - Processzor - Memória - utasításkészlet: - Összeadó: - ADD 100 AC:=AC+100. ADD [100] AC:=AC+Memo[100] Inkrementálás AC:=AC+1. Nullázás AC:=0; Betöltés a regbe LOAD [100] AC:=Memo[100]. Kiírás a memóriába STORE [100] Memo[100]:=AC. Feltétlen ugrás JMP 120 PC:=120; Pl.: 100 LOAD [200] 102 ADD [201] 104 STORE [202] 106 JMP 120

//ez egy memóriahely //azért kettesével növekszik mert 2 byte az utasításhossz I. Utasítás-lehívás (fetch) A PC mindig a következő végrehajtandó utasítás címét tartalmazza. Az utasítás lehívás minden utasítás esetén megegyezik. MAR PC MDR (MAR) IR MDR PC PC+1 II. Utasítás-végrehajtás (execution) - adatbehívás (load) DEC IR MAR DEC címrész IR MDR PC PC+1 - aritmetikai-logikai utasítás, pl. összeadás DEC IR MAR MDR DEC címrész (MAR) 9.oldal Architektúrák II. AC AC AC AC - adattárolás (store) DEC MAR MDR (MAR) - a feltételes ugrás DEC PC AC + MDR vagy AC – MDR vagy AC * MDR vagy AC / MDR IR DEC címrész AC MDR IR DEC címrész Párhuzamos architektúrák Megjelenése: - Nagyszámítógépek esetén a hatvanas években (futószalagos, szuperskalár) - Mikroszámítógépek a nyolcvanas években Párhuzamosság: - Rendelkezésre álló és hasznosított párhuzamosság: o

Rendelkezésre álló az adott programban, illetve általánosabb értelemben az adott feladatban rejlő párhuzamosság o Hasznosított párhuzamosság: a végrehajtás során kihasznált párhuzamosság - Adat -és funkcionális párhuzamosság: o Adatpárhuzamosság: Hasznosíthatjuk speciális (párhuzamos) architektúrával vagy fordítóprogrammal, pl. futószalagos műveletek A másik hasznosítási lehetőség, hogy funkcionális párhuzamossággá alakítjuk, pl.: az adatok feldolgozását ciklusokká fogjuk össze, s a ciklusokat fogjuk párhuzamosan feldolgozni. o Funkcionális párhuzamosság: A feladat logikájában rejlő párhuzamosság mely megjelenik annak formális leírásában: Folyamatábra Adatfolyam-ábra Program A funkcionális párhuzamosság szintjei: Rendelkezésre álló párhuzamosság: o Utasításszinten: az utasítások párhuzamosan végrehajthatók o Ciklusszinten: a ciklusok párhuzamosan végrehajthatók, ha az egyes

iterációkban szereplő adatok függetlenek egymástól (a ciklusmag nem egymásra épül) o Eljárásszinten: Az eljárások párhuzamosan végrehajthatók – feladatfüggő o Programszinten: a programok párhuzamosan végrehajthatók. A többfelhasználós és időosztásos operációs rendszereknél ez megegyezhet a felhasználói szintű párhuzamossággal. Hasznosított párhuzamosság: o Mivel: Architektúrával Operációs rendszerrel Fordítóprogrammal o Szintek: Utasításszintek: architektúrával vagy fordítóprogrammal. 10.oldal Architektúrák II. Szál és folyamatszint: Szál és folyamat a programkód legkisebb önállóan is végrehajtható része, tehát párhuzamosan is feldolgozható. Szál és folyamatszintű párhuzamosság kialakítható: • A programozó által párhuzamos programnyelvek alkalmazásával. Pl.: Occam • Többszálas és többfeladatos operációs rendszerekkel • Párhuzamos fordítóprogramokkal • A

ciklus- és eljárásszintű párhuzamosságot tipikusan szál és folyamatszinten tudjuk hasznosítani Felhasználó szintű párhuzamosság Rendelkezésre álló párhuzamosság Hasznosított párhuzamosság Felhasználói (program) szint Felhasználói szint Eljárásszint Folyamatszint Ciklusszint Szálszint Utasításszint Utasításszint Általában: - Az alacsony szintű párhuzamosságot jellemzően architektúrával illetve fordítóprogrammal hasznosítjuk - A magas szintű párhuzamosságot tipikusan operációs rendszerrel A rendelkezésre álló funkcionális párhuzamos szemcsézettség Finom: Utasításszint (alacsony szintű), Durvább: Ciklus szint, Mély: Eljárás szint, Durva: Felhasználói szint (magas szintű) A párhuzamos architektúrák osztályozása - Flynn féle csoportosítás a hatvanas évekből: o Értelmezett fogalmak: SI – Single Instruction Stream: egyetlen vezérlő egyetlen utasításfolyamot bocsát ki MI – Multiple Instruction

Stream: a vezérlő több, egymástól elkülönülö folyamatot bocsát ki SD – Single Data Stream: A műveletvégző egyetlen adatfolyamot hajt végre, dolgoz fel. MD – Multiple Data Stream: A műveletvégzők több adatfolyamot dolgoz fel. o A fogalmak kombinációi: Az architektúrák: SI, SD: szekvenciális architektúra SIMD: multiple 3D feldolgozás MISD MIMD o Értékelése: Hátránya, hogy nem mutatja Sem a párhuzamosság forrását (adat) Sem pedig a szintjét (szál/utasítás) Javasolt (korszerű) osztályozás Párhuzamos architektúrák: - Adatpárhuzamos architektúrák o Vektorprocesszorok o Asszociatív és neurális architektúrák o SIMD o Szisztolikus architektúrák - Funkcionálisan párhuzamos architektúrák o Utasításszinten párhuzamos architektúrák: Futószalag VLIW: Very Long Instruction Word Szuperskalár o Szálszinten párhuzamos architektúrák o Folyamatszinten párhuzamos architektúrák 11.oldal

Architektúrák II. Utasításszinten párhuzamos architektúrák (Instruction Level Parallelism – ILP) Az ILP architektúrák fő fejlődési útja Neumann-féle Futószalagos szekvenciális (pipeline) architektúra processzorok 1950 1985 Szuperskalár processzorok 1990 Soros kibocsátás, soros végrehajtás Soros kibocsátás, párhuzamos végrehajtás Párhuzamos kibocsátás, párhuzamos végrehajtás Szekvenciális feldolgozás Időbeli párhuzamosság Időbeli párhuzamosság, kibocsátásbeli párhuzamosság Egyetlen processzorban egyetlen, nem futószalagos végrehajtó egység Futószalagos processzor, több, nem futószalagos végrehajtó egységgel Több futószalagos végrehajtó egységet tartalmazó VLIW és szuperskalár processzorok Szuperskalár processzorok MM/3D kiegészítéssel 1994 Párhuzamos kibocsátás, párhuzamos végrehajtás, utasításokon belüli párhuzamosság (SIMD) Időbeli párhuzamosság, kibocsátásbeli párhuzamosság,

utasításon belüli párhuzamosság MM/3D kiegészítéssel rendelkező szuperskalár processzorok 1. 1950 Neumann-féle szekvenciális architektúra: soros kibocsátás és végrehajtás 2. 1985: Futószalag processzorok: Időbeli párhuzamosság Megvalósítási technikái: - Futószalag (időbeli párhuzamosság) - A Többszörözés (térbeli párhuzamosság) A végrehajtó egység szakosodott, pl.: fixpontos / lebegőpontos A futószalag processzorok teljesítményét: - hatékony memória alrendszerrel (gyorsító tárak), és - hatékony ugrás előre jelzéssel juttatták el az ezen az úton elérhető teljesítmény határáig 3. 1990: Kibocsátásbeli párhuzamosság – szuperskalár processzorok - A futószalagos végrehajtó egységeket többszörözték, tehát az időbeli párhuzamossághoz hozzáadódott a térbeli párhuzamosság - Előzmények: o Mivel a többszörözött futószalagelvű végrehajtóegységek óraciklusonként egynél több utasítást is

képesek lettek végrehajtani, a soros kibocsátás szűk keresztmetszetet eredményezett. Ennek feloldására vezették be a párhuzamos kibocsátást 12.oldal Architektúrák II. - Fejlődési irányok: o Statikus ütemezésű VLIW processzorok (egyszerűbb) o Dinamikus ütemezésű szuperskalár processzorok (bonyolultabb) A szuperskalárok fejlődése - Első generációs szuperskalárok: o Közvetlen (nem pufferelt) utasítás-kibocsátás o Elágazásbecslés o Korszerű memória alrendszer - Második generációs szuperskalárok: o Pufferelt (közvetett) utasítás kibocsátás o Regiszter-átnevezés Ezzel az általános célú programok vonatkozásában kimerültek az ILP processzorokban rejlő teljesítménynövelési lehetőségek (ILP). 4. 1995: Utasításbeli párhuzamosság jellemzi: MM/3D kiterjesztés - A SIMD elv alkalmazásával gyorsul a vektorgrafikus műveletvégzés Az ILP feldolgozás technológiája (elvek: pipeline, VLIW, szuperskalár): Futószalag

(pipeline) => Gyakorlati vonatkozás: T – egy termék elkészülésének időtartalma. t – egy egység mennyi ideig van egy munkaállomáson n – futószalagon lévő egységek száma Egyszerre n db készül! (t időközönként egy termék) => Szekvenciális számítógépes feldolgozás: Futószalagos feldolgozás: - Előfeltételei (két fokozatot figyelembe véve): o Két egymástól teljesen független hardver egységet kell kialakítani o Mindkét egység feldolgozási ideje megegyezik o Az egyik egység kimenete lesz a másik bemenete Időbeli párhuzamosság (átlapolás) - Következtetés: Kellően nagy számú utasítás esetén, két hardveregység használva, elvben megduplázódik a feldolgozás sebessége Bontsuk négy részre az utasítás-feldolgozási ciklust: F Fetch D-S/O Decoding – Source Operand E Execution W/B Write Back Ekkor elvben megnégyszereződik az utasítás-feldolgozás sebessége, de a teljesítmény növekedését a függőségek

mérséklik! 13.oldal Architektúrák II. VLIW és szuperskalár processzorok - Hasonlóság: A futószalag elvű végrehajtó egységeket többszörözi: - Különbségek: o Az utasítások felépítése: VLIW: • Hosszú utasítások, melyekben több műveletet írunk elő Keskeny VLIW: 2-4 végrehajtó egység, ~100 bit hosszú utasítások Széles VLIW: 10-20 végrehajtandó egység, többször ~100 bit hosszú utasítások • A célfüggvény, hogy egy utasításban annyi műveletet írjunk elő, ahány végrehajtó egység van • Az utasítások hossza általában a végrehajtó egységek száma, szorozva egy tipikus RISC utasításhosszal (a RISC utasítások jellemzően rövidek, egyforma hosszúak) Szuperskalár: • Hagyományos utasításfolyamot dolgoz fel • Napjainkban ciklusonként 2-6 utasítás hajt végre A gyakorlatban nem közös, hanem adattípusonként különböző (FX, FP és 3D) regisztertárat alkalmaznak napjainkban.

Fejlődési irányok: Evolúciós irány: biztosítja a szoftverkompatibilitást. Pl: az AMD 32 bitről 64 bitesre növelte a sávszélességet és megőrizte a kompatibilitást Revolúciós irány: nem biztosított a szoftver kompatibilitás 14.oldal Architektúrák II. o A függőségek kezelése: VLIW • Statikus függőségkezelés: a compiler végzi • A processzor függőségmentes utasításokat vár el (maga a processzor egyszerűbb) Szuperskalár • Dinamikus függőségkezelés: extra hardverrel • A processzor maga küzdi le a függőségeket (maga a processzor bonyolultabb) A VLIW által igényelt statikus függőségkezelés miatt a processzor egyszerűbb, ezért kb. 20 évvel korábban jelentek meg Másképpen: ugyanazon párhuzamos végrehajtási szinten biztosított: a VLIW processzorok jóval egyszerűbbek, mint a szuperskalár processzorok. Az ILP processzorok iránt támasztott követelmények - A függőségek kezelése - A soros

konzisztencia (következetesség) biztosítása A függőségek fajtái: - Adatfüggőség - Vezérlésfüggőség - Erőforrás-függőség Adatfüggőség - Jellege szerint: o Utasítás szekvencia Valós függőség (RAW – Read After Write) Álfüggőség: • WAR – Write After Read • WAW – Write After Write o Ciklusban - Helye szerint: o Regiszterben o Memóriában Valós adatfüggőség (operandus előrehozás) Probléma: I1 ADD r3r2r1 I2 SHL r3 r3←r2+r1 //shift left Termelő-fogyasztó probléma: az I2 már használni szeretné az r3-regiszte tartalmát, de az még nem készült el A várakozás mérséklése NOP – NO Operation (várakozás) FWD – Forward 15.oldal Architektúrák II. Konklúzió: a valós adatfüggőség káros hatását nem tudjuk kiküszöbölni, csupán mérsékeltük (a példánkban a kétciklusos veszteségünket egy ciklusra csökkentettük). Minden mai processzor alkalmazza Valós (RAW) műveleti adatfüggőségek

mérséklésének általános formája, az operandus előrehozás: Valós (RAW) betöltési adatfüggőség kezelésének általános formája: Ál adat-függőségek RAW Probléma: I1 MUL r3 r2 r1 I2 ADD r2 r4 r5 r3←r2@r1 //nem hajthatjuk végre előbb az I2-t, mert felülírnánk az r2-t Megoldás: regiszter-átnevezés I1 MUL r3 r2 r1 I2 ADD r25 r4 r5 WAW Probléma: I1 mull r3 r2 r1 I2 add r3 r4 r5 Megoldás: regiszter-átnevezés I1 MUL r3 r2 r1 I2 ADD r28 r4 r5 Ciklusbeli adatfüggőségek Probléma: DO 2,n X(I)=A(I)*X(I-1)+B END DO Kezelése: az algoritmus átalakításával Vezérlés-függőségek Feltétlen elágazás – késleltetett ugrás: Probléma: MUL JMP címke ADD címke SHL Mivel a JMP hatására feltétlen ugrás következik be, az ADD utasítás nem hajtódik végre. 16.oldal Architektúrák II. Nem az ADD hanem az SHL a következő (a JMP utáni) utasítás: - feleslegesen hívjuk le az ADD utasítást, sőt - veszélyeztetjük a regiszter-tartalmakat

Kezelése: - utasításrés (buborék) segítségével - Kétfokozatú futószalag: 1 utasításrés - Négyfokozatú futószalag: 3 utasításrés. - n fokozatú futószalag: n-1 utasításrés (a futószalag miatt kell az n-1-edik eredmény a végeredményhez) - Statikusan történik, a compiler által o Egyszerű compiler: minden feltétlen ugrás után beszúr egy NOP-ot (kétfokozatú futószalag esetén) • Értékelés: bár felesleges műveletet végzünk (egy ciklus), de már nem veszélyeztetjük a regiszter-tartalmat o Optimalizáló compiler: • A compiler a JMP utasítás előtt adatmanipuláló utasításokkal kísérli meg feltölteni az utasításrést • Pl.: JMP címke MUL ADD címke SHL • Amennyiben az utasításrés mérete 1 akkor a feltöltés valószínűsége 85%, ha nagyobb, akkor az esély csökken • Ezt a megoldást korai RISC processzorok alkalmazták • Ezzel megszűnt a ciklus-veszteség is! Erőforrás-függőségek Szekvenciális (soros)

konzisztencia: - Az utasítás-feldolgozás soros konzisztenciája: o Az utasítás végrehajtás soros konzisztenciája: processzor-konzisztencia o A memória hozzáférés soros konzisztenciája: memória-konzisztencia Processzor-konzisztencia Probléma: MUL ADD JZ (JMP ZERO) Ha nem figyelünk, akkor a MUL értékére reagál! - Soros feldolgozás esetén, amennyiben az ADD eredménye nulla, akkor ugrik. - Párhuzamos feldolgozás esetén várhatóan a MUL utasítás fejeződik be később, tehát biztosítani kell, hogy az ugrás továbbra is az ADD utasítás nulla eredménye esetén történjen Kivétel-konzisztencia - Gyenge konzisztencia: pontatlan megszakításkezelés - Erős konzisztencia: pontos megszakításkezelés Pontatlan megszakításkezelés Probléma: MUL ADD JZ 17.oldal Architektúrák II. - - Párhuzamos feldolgozás esetén várhatóan az ADD utasítás fejeződik be hamarabb, és lehet, hogy pl. túlcsordulással – amennyiben ezt a processzor elfogadja,

akkor az állapottere elveszti korrektséget, ami csak kiegészítő eljárásokkal lehet helyreállítani. Ennek oka, hogy a korábbi MUL utasítás még definiálatlan s így felborulhat a kivételkezelés soros konzisztenciája Pl.: Power1 (1990) és Power 2 (1993) – csak a lebegőpontos utasításoknál Az Alpha processzorok viszont minden utasításnál Pontos megszakításkezelés - A processzor kizárólag az eredeti utasítás szekvenciának megfelelő sorrendben fogadja el a megszakításkéréseket - Ehhez általában átrendező-puffert használ, így a processzor csak akkor fogadja el a megszakításkérést, amikor az adott utasítást kiírjuk az átrendező-pufferből. Pl: Az Intel processzorcsalád, és a mai processzorok - Az ILP processzorok gyorsítási lehetőségei, avagy a programban rejlő utasításszintű párhuzamossági lehetőségek Az utasításszintű párhuzamosítási lehetőségeket korlátozzák (adat-, vezérlés –és erőforrás f.)

Feltételezzük, hogy eltekinthetünk az erőforrás függőségektől, hogy a processzor regiszterátnevezéssel feloldja az ál adat-függőségeket A valódi adatfüggőséget és a vezérlésfüggőséget kell csak figyelembe venni Az irodalom megkülönbözteti az általános célú programokat (compiler-ek és a nem numerikus feldolgozások), valamint a tudományos célú programokat (lebegőpontos számítások) Az irodalom alapján az általános célú programoknál az ILP gyorsítási lehetőség kétszeres, a tudományos programoknál pedig kétszeres – négyszeres Magyarázat: a feltételes vezérlésátadások alapblokkokra bontják a programot, a párhuzamosítást o csak az alapblokkokon belül vizsgálják, s o az alapblokkok pedig tipikusan rövidek A programokban rejlő utasításszintű párhuzamosság kihasználása - kihasználjuk a ciklusokban rejlő párhuzamosságot o Erre többféle eljárás létezik, pl.: szoftver futószalag L L1 L1 L2 Ln Ciklus L2

Az n-szer kibontott ciklus párhuzamos végrehajtásra előkészítve Az összesített eredmények Ln Az n-szer kibontott ciklus Hátránya: pl.: két darab végrehajtóegység esetén csak maximum kétszeres gyorsítás érhető el, így csak az erőforrás-korláttól függ a gyorsítás mértéke. o A vezérlésfüggőségek problémaköre: Amennyiben 100%-osan meg tudnánk mondani előre a vezérlési utasítások irányát, akkor 10x-100x-os gyorsítást is el tudnánk érni Elvben a program minden ágát is feldolgozhatnánk, azonban csak kétirányú feldolgozásokat feltételezve N darab elágazás esetén 2N darab utat kellene bejárni, ami kezelhetetlenül sok. 18.oldal Architektúrák II. Ennek az elvnek a gyakorlatban használható vetületei: • Megbecsüljük a várható irányt. A feltétel kiértékelésekor o Amennyiben a becslés helyes volt, folytatódik a feldolgozás a megkezdett (helyes) irányba o Amennyiben viszont hibás, a rossz irányba

lehívott utasításokat eldobjuk, s elkezdjük az utasítások lehívását a helyes irányba • Mindkét irányba megindítjuk a feldolgozást, s a feltétel kiértékelése után, a rossz irányba lehívott utasításokat eldobjuk. Az utasításszintű párhuzamosság kihasználásával napjainkban: - általános célú programok esetén mintegy négyszeres, - tudományos műszaki programok esetén 10-20 szoros gyorsítás Időbeli párhuzamosság: futószalagos feldolgozás Fejlődése: - Előlehívás: Az előző utasítás visszaírási fázisát és az aktuális utasítás lehívási fázisát párhuzamosítjuk - o maximum egy óraciklus nyerhetünk, amit a függőségek mérsékelnek o Példa: A hatvanas évek nagyszámítógépeinek egy része A 8086-os mikroprocesszor Csak a végrehajtás fázisban (futószalag-elvű kialakítás): - - Példa: o Nagyszámítógépek: a 60-as évek vektorprocesszoros gépei Mikroszámítógépek: ez a fázis kimaradt A

teljes utasítás-feldolgozási fázisban o Maximum óraciklusonként tudunk feldolgozni egy utasítás, amit a függőségek mérsékelnek o Példa: Nagyszámítógépek (1960) Mikroszámítógépek: 80286 A futószalagos feldolgozás következményei Memóriakezelés: o A memória lassabb, mint a processzor. Hagyományos, szekvenciális elvű 4 ciklusú utasítás: Négyfokozatú futószalag esetén: 19.oldal Architektúrák II. - Míg a hagyományos szekvenciális feldolgozásnál – a példánk esetében – csak minden negyedik óraciklusban kell utasítást lehívni, addig 4 fokozatú futószalagnál már maximum óraciklusonként, amit a függőségek csökkenthetnek. o A memória-alrendszert gyorsításokkal egészítették ki o A gyorsítótárak a 80-as évek második felében terjedtek el robbanásszerűen, a futószalagos feldolgozás terjedésével párhuzamosan Vezérlés-függőségek: o Az okozott teljesítmény-redukció mértéke: Feltétlen

vezérlésátadás esetén az ugrási rés (buborék) mérete N-1, ahol N a futószalag fokozatainak száma Feltételes vezérlésátadás esetén ehhez hozzájön a feltétel kiértékelés, az ugrási cím számítása és a bonyolultabb dekódolás is o A teljesítmény-csökkenés mérséklése: A korai gépekben hardver-kiegészítéssel lehetővé tették, hogy a dekódolás végére előálljon az ugrási cím A korai RISC gépekben késleltetett ugrást alkalmaztak A CISC gépek esetén megjelent: • A fix előrejelzés: A következő végrehajtandó utasítás mindig az ugrási címen helyezkedik el • Az ugrási cím előáll a dekódolási szakasz végére, majd folytatják az utasítások lehívását az ugrási címet követően • A feltételes vezérlés-átadásokban a feltételek kiértékelése az execution szakasz végén következett be: o Az előrejelzés helyes volt s folytatódott az utasítások feldolgozása az elkezdett irányba o Hibás

volt, ekkor az elkezdett utasításokat eldobták és elkezdték a feldolgozást a helyes irányba. Pl: 80486 • Feloldatlan feltételes vezérlési függőség: amikor a feltétel nagy késleltetésű (látenciájú) (szorzás, osztás) utasításra vonatkozik, ami nem hajtódik végre a feltételes vezérlésátadási utasítás execution szakaszának végére ezért blokkolódik a feldolgozás. Pl.: a=x/y if a=1 (várnia kell az előzőre) A futószalagos feldolgozás jellemzői 1. A fokozatok száma: A függőségek miatt sok utasítást kell eldobni! - Pl.: 1980, RISC I. – kétfokozatú, 1982, RISC II – háromfokozatú, napjainkban 15 – 20 fokozat 2. Újrafeldolgozás Újrafeldolgozás nélkül: Újrafeldolgozással, pl.: szorzás, osztás esetén igen hosszú lenne, ha a részeredményeket műveletenként kimentenénk a regiszterekbe. Helyette a részeredményeket az E fokozat végéről visszavezetjük az E fokozat bemenetére. (elemi műveletek sorozata) 20.oldal

Architektúrák II. 3. Operandus-előrehozás 4. Szinkron – aszinkron: napjainkban szinkron az elterjedt A futószalag logikai felépítése 1. szint: A futószalagok funkcionális meghatározása pl.: 2. szint: az egyes fokozatok által végrehajtandó elemi műveletek pl.: Fetch MAR ← PC MDR ← (MAR) IR ← (MDR) PC ← PC+1 A futószalagok fizikai felépítése - általános fizikai felépítés 1960-80 90-es évek (itt jelenik meg a többszörözés): - fizikai megvalósítás: o Univerzális futószalag: minden logikai futószalagot egyetlen fizikai futószalagon valósítunk meg, Pl.: RISC I o Master futószalag (Pentium I.): Két futószalag közül: Az egyik minden utasítás végrehajtására alkalmas, A másik csak az egyszerűbb utasítások végrehajtására képes o Dedikált futószalag, pl.: ProwerPC 604 FX összetett: szorzás, osztás. Képes az újrafeldolgozásra 21.oldal Architektúrák II. Soros konzisztencia (CO): A konzisztencia

biztosítja, hogy az utasítások az eredeti sorrendjüknek megfelelően kerüljenek kiírásra. CISC – RISC futószalagok: A CISC futószalagok jellemzően hosszabbak: - A címszámító fokozat illetve, - A gyorsítótár-elérés miatt Kibocsátásbeli párhuzamosság, szuperskalár processzorok Kibocsátásbeli párhuzamosság: óraciklusonként egynél több utasítást bocsát ki a processzor. 1. Első generációs (keskeny) szuperskalárok Jellemzői: - Közvetlen (nem pufferelt) utasítás-kibocsátás. - Statikus elágazásbecslés: o A programkód jellemzői alapján történik az írás becslése o Pontosabb, mint a fix előrejelzés - A memória-alrendszer kétszintű gyorsítótárat tartalmaz: o L1: A processzorlapkán helyezkedik el Külön adat- és utasítás-gyorsítótár egyportos o L2: Külön lapkákon helyezkedik el Közös gyorsítótár az adatok és az utasítások számára A processzorsínre csatlakozik Közvetlen

utasítás-kibocsátás: Megvalósítása: Utasítás-puffer Működési alternatívák: - Az utasítások sorrendiségének tekintetében o Sorrendben történő kibocsátás: a függő utasítások blokkolják az utasítás-kibocsátást o Sorrenden kívül történő kibocsátás: a függő utasítások nem blokkolják az utasítás-kibocsátást - Az utasítás-ablak feltöltése: o Az utasításokat egyenként pótoljuk o Az utasítások ablak teljes kiürülése után az egészet pótoljuk Tipikus példa az első generációs szuperskalárra: - Sorrendben történő utasítás kibocsátás - Az utasítás-ablak teljes kiürülése után a teljes feltöltése - Az utasítás-ablak 3 db utasítást tartalma - Jelölés: 22.oldal Architektúrák II. Az i-edik ciklusban egyetlen utasítás tudunk kibocsátani, mert az i2 blokkolja a további utasítás kibocsátást. Az i+1 ciklusban időközben feloldódott az i2 függősége, ezért kibocsátható mind az i2, mind pedig az

i3. Az utasítás-ablak ezáltal teljesen kiürül Az i+2 cikusban teljesen feltöltjük az utasítás-ablakot, és két független utasítást tudunk kibocsátani. Az első generációs szuperskalár RISC processzor működési modellje - Az utasítás feldolgozási rendszert alrendszerekre tudjuk bontani, és ezeket külön vizsgálhatjuk - Értelmezhetjük a rendszer átbocsátó-képességét (rátáját, szélességét) A teljes utasítás-feldolgozási rendszer átbocsátási rátáját a legszűkebb keresztmetszetű alrendszer átbocsátási rátája határozza meg Az egyes alkalmazások utasítás-mixe sajátos és távol áll az utasítás feldolgozásának szempontjából ideális utasítás-mixtől minden alkalmazásnak más az átbocsátási rátája - Kibocsátási szűk keresztmetszet - Kezeljük a: o Behívási függőségeket gyorsítótárakkal o A vezérlés-függőségeket statikus elágazás-becsléssel Az adatfüggőségek (a valódi és álfüggőségek)

okoznak főképpen teljesítmény-csökkenést o A tipikus példákból láthatjuk, hogy a 3 utasítás-szélességű ablakból nem mindig sikerül kibocsátani 3 utasítást, a függőségek miatt o A gyakorlatban: RISC esetén 2-3, CISC esetén 2 utasítás feldolgozása történik óraciklusonként o Tehát az első generációs szuperskalárokat keskeny szuperskalároknak nevezzük Jellemző megvalósítások: - Viszonylag általános célú 2 db futószalag (Pentium I) - 2-4 db dedikált futószalag (Alpha 21064) 23.oldal Architektúrák II. Esettanulmány: Pentium I - Processzor o Két futószalag: U (master) futószalag – Minden utasítás feldolgozására (univerzális) V futószalag – csak az Intel által egyszerűnek titulált utasítás feldolgozásra alkalmas o Mindkét futószalag ötfokozatú: F, D, címszámítás, E, W/B. o Csak akkor működik párhuzamosan, ha mindkét futószalag egyszerű utasítást dolgoz fel. Pl: a 10000szer futó

ciklusunk magja egy ADD és egy MOV utasításból áll (mindkettő egyszerű utasítás) Ekkor futószalagosnál 20 ezerszer, szekvenciálisnál 80.000-szer fut le o Az FP utasításokat az U futószalag előfeldolgozza, s magát a számítást egy háromfokozatú, kiegészítő lebegőpontos futószalag végzi. - Memória alrendszer: 2 db, egyenként 8KB méretű utasítás-, ill. adat-gyorsítótárat tartalmaz Második generációs (széles) szuperskalár processzorok Jellemzői: - Dinamikus utasítás-ütemezés - Regiszter-átnevezés Dinamikus utasítás-ütemezés (részei): - Pufferelt utasítás-kibocsátás - Sorrenden kívüli utasítás-végrehajtás Megvalósítása: Működés: - Kibocsátási puffereket alakítottak ki - A kibocsátás során nem történik semmiféle függőség-ellenőrzés (adat, vezérlés, erőforrás-függőséget sem) - A várakoztató-állomásokban addig tartózkodnak az utasítások, amíg függetlenné nem válnak - Minden óraciklusban

ellenőrzésre kerül a várakoztató állomásokban levő összes utasítás függőség szempontjából, és az összes független utasítás kiküldésre kerül, mégpedig sorrenden kívül. - Az utasításablak több tucat utasítást tartalmaz rendkívül kiszélesedett, azaz eltűnt a kibocsátási szűk keresztmetszet Regiszter-átnevezés: - Lényege: minden eredmény-regiszter átnevezésre kerül. Kezeli ennek következményeit is: o Amennyiben később forrásregiszterként hivatkozunk rá, akkor az átnevezési regisztert fogja használni o Amikor egy utasítás-feldolgozás a befejeződött, akkor átmásolja az átnevezési regiszter tartalmát az architekturális regiszterbe, és felszabadítja az átnevezés regisztert. o Hibás elágazásbecslés esetén az átnevezési regiszterek alapján történik a visszajátszás; kezeli a kivételeket is. - A második generációs szuperskalároknál jelent meg, pl.: PowerPC 603 (1993), PentiumPro (1995), Alpha 21264 (1998)

24.oldal Architektúrák II. A második generációs szuperskalár RISC gépek végrehajtási modellje Működése: - Az első rész feladata az utasításablak feltöltése - A forrás-operandusok lehívása architektúrától függően lehet: o kibocsátáshoz kötött vagy o kiküldéshez kötött - A kiküldés során a független utasításokat sorrenden kívül tölti ki - A végrehajtás során az átnevezési regiszterekbe kerülnek az eredmények - Visszaíráskor az eredmények az utasítások eredeti sorrendjében másolódnak át az átnevezési regiszterekből az architekturális regiszterekbe Sávszélesség: - Kibocsátás ráta: 4 utasítás / ciklus - Kiküldési ráta: 5-8 utasítás / ciklus - Végrehajtási ráta: még magasabb Oka: - Bizonyos végrehajtó egységek nem képesek minden ciklusban utasítást fogadni (a bonyolultabb utasítások miatt) - Az utasítás-mix az egyes alkalmazásoknál nem egyezik meg a végrehajtható egységek eloszlásával CISC

gépek: - A CISC processzorok belsejében RISC magot alakítottak ki - A CISC utasítások lefordítják RISC utasításokká - Egy CISC utasításból átlagosan 1,2-1,5 RISC utasítás keletkezik. Mivel a bonyolult CISC utasításokat elhagyták, ezért ezeket valahogy helyettesíteni kell. Pl: for ciklus esetén (bonyolult utasítás): egy if, egy inkrementálás, egy goto és egy ciklus vége utasítás szükséges. - Óraciklusonként ~3 CISC utasítás kerül lehívásra, tehát 3 x (1,2-1,5), azaz ~4 db RISC utasítás kerül kibocsátásra Adatfolyam modell: - Mivel a függőségeket kezeljük csak műveleti és a behívási függőség feloldását kell kivárni - Mihelyt a bemenő operandusok rendelkezésre állnak, a kiküldés elvben bekövetkezhet (erőforrásfüggőség lehetséges), s a végrehajtó egység azonnal működésbe lép (adat-meghajtott elv) 25.oldal Architektúrák II. Esettanulmány: Pentium Pro - ~ 1995-ben jelent meg, induló frekvenciája 133MHz

volt - 14 fokozatú a futószalagja - A dekódolás során történik a CISC utasítások RISC utasításokká való lefordítása, tehát RISC magot tartalmaz - Kibocsátáshoz kötött a forrás-operandus lehívása - 10 db végrehajtó egység, pl.: o 2 db fixpontos, o 1 db lebegőpontos összeadó, o 1 db lebegőpontos szorzó, o 1 db lebegőpontos osztó, o Utasításon belüli párhuzamosság: harmadik generációs szuperskalárok Utasításon belüli párhuzamosság: - Duál műveletes utasítások - SIMD: o Fixpontos (MM) o Lebegőpontos (3D) - VLIW Duál, SIMD: a logikai architektúra kibővítés igényli VLIW: teljesen új logikai architektúrát igényel Duál műveletes utasítások: - Fogalma: egyetlen utasításban kettő darab művelet - Pl.: X=a*b+c (A szorzatok eredményét c-ben felgyűjtjük) LOAD/OP (Betöltés után azonnal elvégzi a műveletet is) - A 70-es években jelentek meg - Numerikus feldolgozásoknál használják, de az általános célúaknál nem

jellemző SIMD: - Fogalma: egyetlen utasításban ugyanazon művelet több operanduson van értelmezve - Fajtái: Fixpontos: ~ 2-8-szoros gyorsítás Lebegőpontos: 2-4-szeres gyorsítás - Ez képezi a processzorok fejlődésének fő irányvonalát: ~ 1994-től - Sajátosságai: o A logikai architektúra módosítást igényel o Az L2 gyorsítótár felkerül a processzor lapkájára o A rendszer-architektúra is módosul: megjelenik az AGP (Accelerated Graphics Port) VLIW: - Fogalma: egyetlen utasításokban sok műveletet írunk elő - Korai VLIW-ek: o Igen hosszú utasítások, pl.: a TRACE VLIW processzor esetén: 256-1024 bites utasítások 7-28 műveletet tartalmaz o A statikus ütemezés során a compiler gondoskodik a függőségek feloldásáról o A compiler szoros kapcsolatban áll a fizikai architektúrával, pl.: ismernie kell a végrehajtó egységek számát, azok késleltetését, a behívási késleltetést, stb. o A 80-as évek első felében papíron,

második felében a piacon is megjelentek (pl.: TRACE) o Gyorsan leállt a forgalmazásuk, mivel a compiler túlságosan kötődött a fizikai architektúrához 26.oldal Architektúrák II. - Mai VLIW-ek: o A compilerek fejlődtek, ezért a 90-es évek végén újra megjelentek o Szerverek piaca: INTEL Itanium: 6 db végrehajtó egységgel rendelkezik A szuperskalárok 4 db / ciklus feldolgozási rátáját kívánják a 6 db végrehajtó egységgel túlszárnyalni o Hordozható gépek piaca: a Transmeta cég processzorai: A statikus ütemezés egyszerűbb processzort eredményez kisebb áramfogyasztás (2W DVD-lejátszás közben!) Fajtái: • 4 db végrehajtó egységgel • 8 db végrehajtó egységgel Rendszer-architektúra A sínrendszer osztályozása szintek szerint: - Egyszintű sínrendszer, pl.: az első IBM PC - Kétszintű sínrendszer: o Megjelenésének oka: A processzor órafrekvenciája nőtt, a bővítősíné viszont maradt a régi -

Háromszintű sínrendszer (helyi sín): o Megjelenésének oka: a multimédiás alkalmazásokhoz gyorsabb perifériák jelentek meg (winchester, videokártya), melyek teljesítményét a régi sínrendszer szűk keresztmetszete miatt nem lehetett kihasználni - Négysínes színrendszer: o Megjelenésének oka: a multimédiás alkalmazások a videokártya további gyorsítását igényelték o AGP (mivel csak egyetlen ajzat, nem tekinthető igazi sínnek) Rugalmas szintezésű sínrendszer: o A szerverpiacra szánták o Kapcsolókat alkalmaznak, melyek segítségével ideiglenes dedikált kapcsolatok jönnek létre az egyes egységek között - Készítették: Andó Mihály (szöveg) Vincze István (képek) Fábián Zoltán (hibaellenőrzés) 27.oldal Architektúrák II

választhatnak - A szervizek számára a hibajavítás egyszerűbb lett, a kártyákat ki lehetett cserélni A sín felhasználói: - A sín használatát az aktív eszköz (master) kezdeményezi - A processzor a leggyakoribb master - A szerepváltozó: a) A processzor (master) felkéri a DMA vezérlőt (slave) egy DMA átvitel lebonyolítására b) Utána a DMA vezérlő (master) felkéri a memóriát (slave) a DMA átvitelben való részvételre Master Slave Értelmezés processzor memória utasítás vagy adatlehívás processzor I/O vezérlő adatátvitel lebonyolítására processzor co-processzor lebegőpontos művelet végrehajtása I/O vezérlő memória adatátvitel co-processzor memória lebegőpontos műveletvégzés A memória sohasem lehet master! A sínrendszeren belüli címzés - Az aktív (master) eszköz címmel jelöli ki a kommunikációban résztvevő passzív eszközt (slave). a) A cím magasabb helyértékű bitjei jelöli ki a slave eszközt b) Az alacsonyabb

helyértékű bitek pedig az eszközön belüli helyet (adatot) Címzés: - Logikai eszközcímzés: a) Az adott vezérlőkártyához az installálási folyamat során az embernek kellett címet rendelni. b) Ezt a módszert használják a hagyományos vezérlőkártyáknál (ISA) - Geográfiai eszközcímzés: a) Az aljzatokhoz vannak a címek hozzárendelve b) Ezt használjuk a mai vezérlőkártyák (pl.: PCI), mivel így az operációs rendszer végzi el az installálást (plug and play) A címzettek száma: - A címzés maga a címvezeték segítségével történik. Az átvitel során tipikusan egy adó és egy vevő aktív, de lehetséges az egy adó és több vevő eset is - Szórási (broadcast) címzés: az összes egység egyidejű megcímzése a) pl.: Reset (valamennyi egység kezdeti állapotba hozása) b) Erre a célra alkalmazhatunk speciális címet, pl.: nulla címet c) Csoportcímzés (multicasting): Alkalmazhatunk egy erre szolgáló szórási vezérlővonalat is:

ebben az esetben a címvezetéken kijelölhetjük azt a kört amelynek a címzés szól 1.oldal Architektúrák II. A sínrendszer működése Megosztott sínrendszer esetén két fázisból áll: - A sínfoglalás (bus arbitration) – ha két vagy több egység szeretne master lenni, akkor sínütemezésre van szükség, hogy a káoszt elkerüljük - A sínhasználat (bus timing) – maga az adatátvitel folyamata A sínfoglalás Soros sínfoglalás: - Hardver lekérdezéses (daisy chain – gyermekláncfű). Előnyei: a) Kevés vezetéket igényel (olcsó) b) Elvben végtelen számú egységet tudunk csatlakoztatni Hátrányai: c) A prioritás hardveres úton szabályozott (merev) d) Az előrébb álló egységek elnyomhatják a hátrébb állókat e) Érzékeny a bus grant vonal meghibásodására Működése: Amikor az ütemező egy sínkérést észlel, használati engedélyt ad ki oly módon, hogy beállítja a sínhasználat engedélyezése jelet. Ez sorban keresztülfut

az összes egységen Amikor az ütemezőhöz fizikailag legközelebbi eszköz meglátja az engedélyezést, ellenőrzi, hogy ő adta-e ki a kérést. Ha igen, akkor átveszi a sínt, és nem továbbítja az engedélyt a következő eszköznek. Az egységek távolsága egyben a prioritásukat is meghatározza. - Szoftver lekérdezéses (software polling). Előnyei: a) A prioritás szoftveres úton szabályozott (rugalmas) b) Kevésbé érzékeny a bus grant vonal meghibásodására Hátrányai: c) több vezérlővonal (drága) d) A csatlakoztatható egységek számát a bus grant vonalak száma korlátozza, példánkban maximum 23=8 db 2.oldal Architektúrák II. Párhuzamos sínfoglaltság: a) Előnye: gyors b) Hátránya: még több vezérlővonalat igényel (még drágább), pl.: PCI Rejtett sínfoglalás: - Előfeltétele: két, egymástól független hardver vezérelje a sínfoglalást és az adatátvitelt - Amíg az aktuális adatátvitel folyik, az alatt lehetőség van

az adatsín következő használójának kiválasztására Az adatátvitel (bus timing) Szinkron adatátvitel - Fogalma: Az adatátvitel mind az adó, mind a vevő számára előre ismert időintervallumban történik - Óra-ütemadó: a) Mind az adó, mind a vevő közös forrásból kapja az órajelet (akkor alkalmazzák, ha kicsi a távolság az adó, és a vevő között) b) Mind az adónak, mind a vevőnek saját, de azonos frekvenciával járó óra-ütemadója van. Ezek időben elcsúszhatnak egymástól, ezért egy szinkronjel segítségével hangolják össze a működésüket Értékelése: - Előnye: olcsó, egyszerű a megvalósítása - Hátrány: Az előre ismert idő intervallum hosszát mindig a leglassúbb egység határozza meg ez visszafogja a gyors egységeket (ez kiküszöbölhető többszintű sínrendszer alkalmazásával, ahol átviteli-sebesség függő tartományonként csoportosítják az egységeket) A Bővítősínek fajtái: - Átviteli sebesség szerint

(szinkron meghajtású sínek): a) Kompatibilitási vagy hagyományos sín (~ 5MB/s) b) Helyi sín, pl.: PCI (lehet 132 vagy 264 MB/s) c) AGP 1x (500 MB/s) - Tervezési szempontok szerint: a) Platformfüggő, pl.: ISA, EISA b) Platformfüggetlen, pl.: USB, SCSI, PCI Aszinkron adatátvitel Fogalma: Az előző elemi művelet befejeződése egyben jelzés a következő elemi művelet kezdetére. Fajtái: - Egyvezetékes (egy vezérlővezeték) a) Adó oldali vezérlés: Először az adat az adatsínre kerül, majd késleltetést alkalmazunk. Hátránya: Az adónak nincs visszacsatolása arról, hogy a vevő valóban elolvasta-e az adatsínre helyezett adatot. Lehet, hogy a vevő ki van kapcsolva (Jobbra az alsó ábrán: Data; Data ready) 3.oldal Architektúrák II. - b) Vevő oldali vezérlés: Ez biztonságosabb átvitelt jelent, mert a vevő az átvitel igénylésének pillanatában aktív, de továbbra sincs visszacsatolás az adat célba érkezéséről. (Jobbra az alsó

ábrán: Data; Data request) Kétvezetékes átvitel (handshaking - kézfogás) a) Adó oldali vezérlés: az alsó ábrán Data, Data Ready, Data Acknowledge b) Vevő oldali vezérlés: az alsó ábrán Data, Data Request, Data Ready Az I/O rendszer Fogalma: a processzor-memória együttest a külvilággal összekapcsoló rendszer. Értelmezése: Fejlődése: - A processzor közvetlenül irányította a perifériákat Elkülönült I/O modul vezérli a perifériákat: lekérdezéses I/O (wait for flag) Elkülönült I/O modul vezérli a perifériákat: megszakításos I/O A DMA megjelenése – önállóan végzi az átvitel vezérlését Csatorna: I/O célú utasításokat dolgoz fel, közben a központi operatív tárat használja I/O processzor: I/O célú utasításokat dolgoz fel, saját operatív tárral (memóriával) rendelkezik. - A processzor közreműködésével (programozott I/O): a) Címtér: 1. Különálló I/O címtér 2. Memóriába leképezett I/O címtér b)

Működés: 1. Feltételes 2. Feltétlen Processzor közreműködése nélkül: a) DMA b) Csatorna c) I/O processzor Rendszer: - 4.oldal Architektúrák II. Programozott I/O Fogalma: minden egyes I/O művelethez a processzornak egy-egy utasítást kell végrehajtania Fajtái címtér szerint: Különálló I/O címtér. - Elve: A processzor két különálló címteret lát. - - Jellemzői: a) A címsín szolgál: 1. az operatív tár, 2. és az I/O egység címzésére b) Létezik olyan vezérlővonal (memória / I/O) mely megmutatja, hogy az adott időpillanatban a címsínen memória vagy I/O cím található c) mivel két különálló címtérről van szó, ugyanaz a cím szerepelhet memóriacímként és I/O címként is. d) Pl.: Intel esetében az eszköz 16 biten címezhető meg (65536 féle I/O cím) e) azon regisztereket, amelyeken keresztül a processzor a perifériákkal kommunikálhat, I/O portnak nevezzük, amely fizikailag a vezérlőkártyán helyezkedik el

Az I/O Port regiszterei: a) Parancs (command) regiszter, amelybe a processzor írhatja a kívánságait a perifériákhoz b) Adat (data) regiszter 1. Data input regiszter: ebből olvassa a processzor a perifériától kapott adatokat 2. Data output regiszter: ebbe írja a processzor a periféria számára küldött adatokat c) Állapot (Status) regiszter: innen olvassa a processzor a periféria üzeneteit d) Az input, output regisztereket a mai gyakorlatban összevonják: parancs állapot regiszter, adat input-output regiszter. e) Napjainkban az I/O porton belül több regiszter is található, pl.: 1. I/O egység működőképességét jelző regiszter 2. I/O egység típusát, konfigurációs jellemzőit tároló regiszter (plug & play) 3. a nagyobb teljesítményű, összetettebb I/O egységeknél több parancs-, adat-, és állapotregiszter lehetséges A különálló I/O címtér megvalósítása: - Következmény: a) Különálló utasítások szolgálnak a

memória-műveletekre (pl.: load/store), és b) Különálló utasítások szolgálnak az I/O műveletekre. Pl: Intel esetében 1. inX: a processzor olvassa be az X című I/O port adatregiszterét az AC-ba outX: a processzor beírja az AC tartalmát az X című I/O port adatregiszterébe 5.oldal Architektúrák II. - Értékelés: a) Előnyei: egyszerű, olcsó a megvalósítása b) Hátránya: a processzor részt vesz az I/O műveletekben szűk keresztmetszet c) az AC szűk keresztmetszetet jelent nagy tömegű I/O számára d) Pl.: Hálókártya (ISA), amely az IBM PC-nél különálló IO címtérrel rendelkezik e) Minden mai piacon lévő processzorban megtalálható A Memóriára leképzett I/O (Memory mapped I/O) Elve: Ezt látja a processzor Processzor Ezt az I/O egység látja Jellemzői: - A megosztás: a processzor memóriakezelő utasítással (load-store) éri el azt a közös memóriaterületet, amit a periféria is kezelhet Ebben az esetben az I/O egység

használhatja a rendszersínt nagyobb az átviteli sebesség Megvalósítása: Értékelése: - Jóval gyorsabb, mint a különálló I/O címtér (előny) Minden I/O esetén a processzornak egy utasítást végre kell hajtania (hátrány) Pl.: Az IBM PC-nél a képernyőkezelés Működése: Feltétlen átvitel: - A vevő mindig vételre kész állapotban van - Nem ellenőrizzük az átvitel sikerességét - Nincs szinkronizálás a vevő és az adó között. - Pl.: LED Feltételes átvitel: - Lekérdezés (wait for flag) a) A processzor beírja a kívánságát az I/O port parancsregiszterébe b) A processzor kiolvassa az I/O egység állapotregiszterének tartalmát c) Amennyiben nem „ready”, akkor vissza a (b) pontra d) Amennyiben „ready”, akkor kiolvassa az I/O egység adott adatregiszterének tartalmát, majd beírja azt az akkumulátorba (AC) Értékelése: A processzor - I/O egység közti sebességkülönbség miatt a processzor akár több milliószor olvassa be

feleslegesen az állapotregiszter tartalmát - Megszakításos: a) A processzor beírja a kívánságát az I/O egység parancsregiszterébe, majd elkezd mást csinálni 6.oldal Architektúrák II. b) Amikor az I/O egység begyűjtötte a perifériától a szükséges adatot az adatregiszterben: 1. Beállítja az állapot regiszter „ready” bitjét, és 2. Megszakításkérést küld a processzor felé c) A processzor a következő utasítás-töréspontban elkezdheti a megszakításkérés feldolgozását 1. Beolvassa az I/O egység állapotregiszterét 2. ha ott a „ready” bit be van állítva, akkor egy ennek megfelelő megszakításfeldolgozó programot indít el; ez kiolvassa az I/O port adatregiszterét és tartalmát átviszi az AC-ba DMA – Direct Memory Access Fogalma: nagy tömegű adat gyors periféria alkalmazásával történő átvitele, a processzor közreműködése nélkül Elve: Megvalósítása: DC – decrementer I/O AR – I/O Address Register I/O DR

– I/O Data Register Működése: - a DMA vezérlő „felprogramozása”: programozott I/O-val átvisszük a processzorból a DMA vezérlőbe az átvitelt leíró alapinformációkat: a) A DC-be beírjuk az átviendő adategységek számát b) Az I/O AR-be beírjuk az átviendő memóriablokk kezdőcímét c) Az adatátviteli egysége (byte, félszó, szó) d) Az átvitel irányát e) A résztvevő periféria címét, és a DMA vezérlő címét f) Az átvitel módját blokkos vagy cikluslopásos módon 7.oldal Architektúrák II. - Blokkos vagy (burst) üzemmód (pl.: Winchester esetén memóriacím-inkrementálás) a) Mihelyt a DMA vezérlő előkészítette az első átviendő adatelemet az I/O DR-ben, akkor egy DMA request jelzést küld a processzornak. Ezzel kéri a rendszersín használati jogát! b) A processzor DMA acknowledge jelzéssel lemond a rendszersín használati jogáról c) A DMA vezérlő beírja az I/O DR tartalmát az I/O AR által kijelölt

memóriacímre, majd a DC értékét csökkenti, az I/O AR értékét növeli d) Ez a ciklus addig fut, míg a DC értéke nullára nem csökken - Cikluslopásos (cycle stealing) átvitel Értékelése: Míg az utasítás-töréspontban a megszakítás feldolgozással a processzorra további munka várhat, addig a DMA töréspontban a DMA vezérlő a processzor helyet dolgozhat. Csatorna - A DMA koncepciójának kiterjesztése a lassúbb perifériákra A processzor és a csatorna közös operatív tárat használ. A memóriában lévő I/O utasításokat a csatorna, nem pedig a processzor hajtja végre. Továbbra is vannak I/O egységek, azonban ezek munkáját a csatorna fogja össze, a processzor helyett. Fajtái: - - Szelektor csatorna a) a gyorsabb egységeket fogja össze b) Közülük mindig csak egy kommunikálhat egyszerre c) Megvalósítása: ábra Multiplex csatorna: a) A lassúbb egységeket fogja össze b) Közülük több kommunikálhat egyszerre c)

Megvalósítása: ábra d) Fajtái: 1. Bájt multiplexer: az átvitel során a legnagyobb sebesség elérése a cél Pl.: 3 egység kommunikációja esetén: Aegység=A1, A2, A3, A4, Begység= B1, B2, B3, B4, Karakter sorozata Cegység= C1, C2, C3, C4, Eredő adatfolyam: A1 B1 C1 A2 C2 A3 B2 C3 A4 C4 A5 B3 C5. 2. Blokk multiplexer: a byte multiplexerhez hasonlóan blokkszinten végzi a munkáját. Pl: IBM 360-as gépcsalád 8.oldal Architektúrák II. Egy hipotetikus számítógép tervezése Korlátaink – jellemzők: - minden utasítás két byte hosszú (256 lehetséges cím): MK címrész 1 byte 1 byte - két egységből áll - Processzor - Memória - utasításkészlet: - Összeadó: - ADD 100 AC:=AC+100. ADD [100] AC:=AC+Memo[100] Inkrementálás AC:=AC+1. Nullázás AC:=0; Betöltés a regbe LOAD [100] AC:=Memo[100]. Kiírás a memóriába STORE [100] Memo[100]:=AC. Feltétlen ugrás JMP 120 PC:=120; Pl.: 100 LOAD [200] 102 ADD [201] 104 STORE [202] 106 JMP 120

//ez egy memóriahely //azért kettesével növekszik mert 2 byte az utasításhossz I. Utasítás-lehívás (fetch) A PC mindig a következő végrehajtandó utasítás címét tartalmazza. Az utasítás lehívás minden utasítás esetén megegyezik. MAR PC MDR (MAR) IR MDR PC PC+1 II. Utasítás-végrehajtás (execution) - adatbehívás (load) DEC IR MAR DEC címrész IR MDR PC PC+1 - aritmetikai-logikai utasítás, pl. összeadás DEC IR MAR MDR DEC címrész (MAR) 9.oldal Architektúrák II. AC AC AC AC - adattárolás (store) DEC MAR MDR (MAR) - a feltételes ugrás DEC PC AC + MDR vagy AC – MDR vagy AC * MDR vagy AC / MDR IR DEC címrész AC MDR IR DEC címrész Párhuzamos architektúrák Megjelenése: - Nagyszámítógépek esetén a hatvanas években (futószalagos, szuperskalár) - Mikroszámítógépek a nyolcvanas években Párhuzamosság: - Rendelkezésre álló és hasznosított párhuzamosság: o

Rendelkezésre álló az adott programban, illetve általánosabb értelemben az adott feladatban rejlő párhuzamosság o Hasznosított párhuzamosság: a végrehajtás során kihasznált párhuzamosság - Adat -és funkcionális párhuzamosság: o Adatpárhuzamosság: Hasznosíthatjuk speciális (párhuzamos) architektúrával vagy fordítóprogrammal, pl. futószalagos műveletek A másik hasznosítási lehetőség, hogy funkcionális párhuzamossággá alakítjuk, pl.: az adatok feldolgozását ciklusokká fogjuk össze, s a ciklusokat fogjuk párhuzamosan feldolgozni. o Funkcionális párhuzamosság: A feladat logikájában rejlő párhuzamosság mely megjelenik annak formális leírásában: Folyamatábra Adatfolyam-ábra Program A funkcionális párhuzamosság szintjei: Rendelkezésre álló párhuzamosság: o Utasításszinten: az utasítások párhuzamosan végrehajthatók o Ciklusszinten: a ciklusok párhuzamosan végrehajthatók, ha az egyes

iterációkban szereplő adatok függetlenek egymástól (a ciklusmag nem egymásra épül) o Eljárásszinten: Az eljárások párhuzamosan végrehajthatók – feladatfüggő o Programszinten: a programok párhuzamosan végrehajthatók. A többfelhasználós és időosztásos operációs rendszereknél ez megegyezhet a felhasználói szintű párhuzamossággal. Hasznosított párhuzamosság: o Mivel: Architektúrával Operációs rendszerrel Fordítóprogrammal o Szintek: Utasításszintek: architektúrával vagy fordítóprogrammal. 10.oldal Architektúrák II. Szál és folyamatszint: Szál és folyamat a programkód legkisebb önállóan is végrehajtható része, tehát párhuzamosan is feldolgozható. Szál és folyamatszintű párhuzamosság kialakítható: • A programozó által párhuzamos programnyelvek alkalmazásával. Pl.: Occam • Többszálas és többfeladatos operációs rendszerekkel • Párhuzamos fordítóprogramokkal • A

ciklus- és eljárásszintű párhuzamosságot tipikusan szál és folyamatszinten tudjuk hasznosítani Felhasználó szintű párhuzamosság Rendelkezésre álló párhuzamosság Hasznosított párhuzamosság Felhasználói (program) szint Felhasználói szint Eljárásszint Folyamatszint Ciklusszint Szálszint Utasításszint Utasításszint Általában: - Az alacsony szintű párhuzamosságot jellemzően architektúrával illetve fordítóprogrammal hasznosítjuk - A magas szintű párhuzamosságot tipikusan operációs rendszerrel A rendelkezésre álló funkcionális párhuzamos szemcsézettség Finom: Utasításszint (alacsony szintű), Durvább: Ciklus szint, Mély: Eljárás szint, Durva: Felhasználói szint (magas szintű) A párhuzamos architektúrák osztályozása - Flynn féle csoportosítás a hatvanas évekből: o Értelmezett fogalmak: SI – Single Instruction Stream: egyetlen vezérlő egyetlen utasításfolyamot bocsát ki MI – Multiple Instruction

Stream: a vezérlő több, egymástól elkülönülö folyamatot bocsát ki SD – Single Data Stream: A műveletvégző egyetlen adatfolyamot hajt végre, dolgoz fel. MD – Multiple Data Stream: A műveletvégzők több adatfolyamot dolgoz fel. o A fogalmak kombinációi: Az architektúrák: SI, SD: szekvenciális architektúra SIMD: multiple 3D feldolgozás MISD MIMD o Értékelése: Hátránya, hogy nem mutatja Sem a párhuzamosság forrását (adat) Sem pedig a szintjét (szál/utasítás) Javasolt (korszerű) osztályozás Párhuzamos architektúrák: - Adatpárhuzamos architektúrák o Vektorprocesszorok o Asszociatív és neurális architektúrák o SIMD o Szisztolikus architektúrák - Funkcionálisan párhuzamos architektúrák o Utasításszinten párhuzamos architektúrák: Futószalag VLIW: Very Long Instruction Word Szuperskalár o Szálszinten párhuzamos architektúrák o Folyamatszinten párhuzamos architektúrák 11.oldal

Architektúrák II. Utasításszinten párhuzamos architektúrák (Instruction Level Parallelism – ILP) Az ILP architektúrák fő fejlődési útja Neumann-féle Futószalagos szekvenciális (pipeline) architektúra processzorok 1950 1985 Szuperskalár processzorok 1990 Soros kibocsátás, soros végrehajtás Soros kibocsátás, párhuzamos végrehajtás Párhuzamos kibocsátás, párhuzamos végrehajtás Szekvenciális feldolgozás Időbeli párhuzamosság Időbeli párhuzamosság, kibocsátásbeli párhuzamosság Egyetlen processzorban egyetlen, nem futószalagos végrehajtó egység Futószalagos processzor, több, nem futószalagos végrehajtó egységgel Több futószalagos végrehajtó egységet tartalmazó VLIW és szuperskalár processzorok Szuperskalár processzorok MM/3D kiegészítéssel 1994 Párhuzamos kibocsátás, párhuzamos végrehajtás, utasításokon belüli párhuzamosság (SIMD) Időbeli párhuzamosság, kibocsátásbeli párhuzamosság,

utasításon belüli párhuzamosság MM/3D kiegészítéssel rendelkező szuperskalár processzorok 1. 1950 Neumann-féle szekvenciális architektúra: soros kibocsátás és végrehajtás 2. 1985: Futószalag processzorok: Időbeli párhuzamosság Megvalósítási technikái: - Futószalag (időbeli párhuzamosság) - A Többszörözés (térbeli párhuzamosság) A végrehajtó egység szakosodott, pl.: fixpontos / lebegőpontos A futószalag processzorok teljesítményét: - hatékony memória alrendszerrel (gyorsító tárak), és - hatékony ugrás előre jelzéssel juttatták el az ezen az úton elérhető teljesítmény határáig 3. 1990: Kibocsátásbeli párhuzamosság – szuperskalár processzorok - A futószalagos végrehajtó egységeket többszörözték, tehát az időbeli párhuzamossághoz hozzáadódott a térbeli párhuzamosság - Előzmények: o Mivel a többszörözött futószalagelvű végrehajtóegységek óraciklusonként egynél több utasítást is

képesek lettek végrehajtani, a soros kibocsátás szűk keresztmetszetet eredményezett. Ennek feloldására vezették be a párhuzamos kibocsátást 12.oldal Architektúrák II. - Fejlődési irányok: o Statikus ütemezésű VLIW processzorok (egyszerűbb) o Dinamikus ütemezésű szuperskalár processzorok (bonyolultabb) A szuperskalárok fejlődése - Első generációs szuperskalárok: o Közvetlen (nem pufferelt) utasítás-kibocsátás o Elágazásbecslés o Korszerű memória alrendszer - Második generációs szuperskalárok: o Pufferelt (közvetett) utasítás kibocsátás o Regiszter-átnevezés Ezzel az általános célú programok vonatkozásában kimerültek az ILP processzorokban rejlő teljesítménynövelési lehetőségek (ILP). 4. 1995: Utasításbeli párhuzamosság jellemzi: MM/3D kiterjesztés - A SIMD elv alkalmazásával gyorsul a vektorgrafikus műveletvégzés Az ILP feldolgozás technológiája (elvek: pipeline, VLIW, szuperskalár): Futószalag

(pipeline) => Gyakorlati vonatkozás: T – egy termék elkészülésének időtartalma. t – egy egység mennyi ideig van egy munkaállomáson n – futószalagon lévő egységek száma Egyszerre n db készül! (t időközönként egy termék) => Szekvenciális számítógépes feldolgozás: Futószalagos feldolgozás: - Előfeltételei (két fokozatot figyelembe véve): o Két egymástól teljesen független hardver egységet kell kialakítani o Mindkét egység feldolgozási ideje megegyezik o Az egyik egység kimenete lesz a másik bemenete Időbeli párhuzamosság (átlapolás) - Következtetés: Kellően nagy számú utasítás esetén, két hardveregység használva, elvben megduplázódik a feldolgozás sebessége Bontsuk négy részre az utasítás-feldolgozási ciklust: F Fetch D-S/O Decoding – Source Operand E Execution W/B Write Back Ekkor elvben megnégyszereződik az utasítás-feldolgozás sebessége, de a teljesítmény növekedését a függőségek

mérséklik! 13.oldal Architektúrák II. VLIW és szuperskalár processzorok - Hasonlóság: A futószalag elvű végrehajtó egységeket többszörözi: - Különbségek: o Az utasítások felépítése: VLIW: • Hosszú utasítások, melyekben több műveletet írunk elő Keskeny VLIW: 2-4 végrehajtó egység, ~100 bit hosszú utasítások Széles VLIW: 10-20 végrehajtandó egység, többször ~100 bit hosszú utasítások • A célfüggvény, hogy egy utasításban annyi műveletet írjunk elő, ahány végrehajtó egység van • Az utasítások hossza általában a végrehajtó egységek száma, szorozva egy tipikus RISC utasításhosszal (a RISC utasítások jellemzően rövidek, egyforma hosszúak) Szuperskalár: • Hagyományos utasításfolyamot dolgoz fel • Napjainkban ciklusonként 2-6 utasítás hajt végre A gyakorlatban nem közös, hanem adattípusonként különböző (FX, FP és 3D) regisztertárat alkalmaznak napjainkban.

Fejlődési irányok: Evolúciós irány: biztosítja a szoftverkompatibilitást. Pl: az AMD 32 bitről 64 bitesre növelte a sávszélességet és megőrizte a kompatibilitást Revolúciós irány: nem biztosított a szoftver kompatibilitás 14.oldal Architektúrák II. o A függőségek kezelése: VLIW • Statikus függőségkezelés: a compiler végzi • A processzor függőségmentes utasításokat vár el (maga a processzor egyszerűbb) Szuperskalár • Dinamikus függőségkezelés: extra hardverrel • A processzor maga küzdi le a függőségeket (maga a processzor bonyolultabb) A VLIW által igényelt statikus függőségkezelés miatt a processzor egyszerűbb, ezért kb. 20 évvel korábban jelentek meg Másképpen: ugyanazon párhuzamos végrehajtási szinten biztosított: a VLIW processzorok jóval egyszerűbbek, mint a szuperskalár processzorok. Az ILP processzorok iránt támasztott követelmények - A függőségek kezelése - A soros

konzisztencia (következetesség) biztosítása A függőségek fajtái: - Adatfüggőség - Vezérlésfüggőség - Erőforrás-függőség Adatfüggőség - Jellege szerint: o Utasítás szekvencia Valós függőség (RAW – Read After Write) Álfüggőség: • WAR – Write After Read • WAW – Write After Write o Ciklusban - Helye szerint: o Regiszterben o Memóriában Valós adatfüggőség (operandus előrehozás) Probléma: I1 ADD r3r2r1 I2 SHL r3 r3←r2+r1 //shift left Termelő-fogyasztó probléma: az I2 már használni szeretné az r3-regiszte tartalmát, de az még nem készült el A várakozás mérséklése NOP – NO Operation (várakozás) FWD – Forward 15.oldal Architektúrák II. Konklúzió: a valós adatfüggőség káros hatását nem tudjuk kiküszöbölni, csupán mérsékeltük (a példánkban a kétciklusos veszteségünket egy ciklusra csökkentettük). Minden mai processzor alkalmazza Valós (RAW) műveleti adatfüggőségek

mérséklésének általános formája, az operandus előrehozás: Valós (RAW) betöltési adatfüggőség kezelésének általános formája: Ál adat-függőségek RAW Probléma: I1 MUL r3 r2 r1 I2 ADD r2 r4 r5 r3←r2@r1 //nem hajthatjuk végre előbb az I2-t, mert felülírnánk az r2-t Megoldás: regiszter-átnevezés I1 MUL r3 r2 r1 I2 ADD r25 r4 r5 WAW Probléma: I1 mull r3 r2 r1 I2 add r3 r4 r5 Megoldás: regiszter-átnevezés I1 MUL r3 r2 r1 I2 ADD r28 r4 r5 Ciklusbeli adatfüggőségek Probléma: DO 2,n X(I)=A(I)*X(I-1)+B END DO Kezelése: az algoritmus átalakításával Vezérlés-függőségek Feltétlen elágazás – késleltetett ugrás: Probléma: MUL JMP címke ADD címke SHL Mivel a JMP hatására feltétlen ugrás következik be, az ADD utasítás nem hajtódik végre. 16.oldal Architektúrák II. Nem az ADD hanem az SHL a következő (a JMP utáni) utasítás: - feleslegesen hívjuk le az ADD utasítást, sőt - veszélyeztetjük a regiszter-tartalmakat

Kezelése: - utasításrés (buborék) segítségével - Kétfokozatú futószalag: 1 utasításrés - Négyfokozatú futószalag: 3 utasításrés. - n fokozatú futószalag: n-1 utasításrés (a futószalag miatt kell az n-1-edik eredmény a végeredményhez) - Statikusan történik, a compiler által o Egyszerű compiler: minden feltétlen ugrás után beszúr egy NOP-ot (kétfokozatú futószalag esetén) • Értékelés: bár felesleges műveletet végzünk (egy ciklus), de már nem veszélyeztetjük a regiszter-tartalmat o Optimalizáló compiler: • A compiler a JMP utasítás előtt adatmanipuláló utasításokkal kísérli meg feltölteni az utasításrést • Pl.: JMP címke MUL ADD címke SHL • Amennyiben az utasításrés mérete 1 akkor a feltöltés valószínűsége 85%, ha nagyobb, akkor az esély csökken • Ezt a megoldást korai RISC processzorok alkalmazták • Ezzel megszűnt a ciklus-veszteség is! Erőforrás-függőségek Szekvenciális (soros)

konzisztencia: - Az utasítás-feldolgozás soros konzisztenciája: o Az utasítás végrehajtás soros konzisztenciája: processzor-konzisztencia o A memória hozzáférés soros konzisztenciája: memória-konzisztencia Processzor-konzisztencia Probléma: MUL ADD JZ (JMP ZERO) Ha nem figyelünk, akkor a MUL értékére reagál! - Soros feldolgozás esetén, amennyiben az ADD eredménye nulla, akkor ugrik. - Párhuzamos feldolgozás esetén várhatóan a MUL utasítás fejeződik be később, tehát biztosítani kell, hogy az ugrás továbbra is az ADD utasítás nulla eredménye esetén történjen Kivétel-konzisztencia - Gyenge konzisztencia: pontatlan megszakításkezelés - Erős konzisztencia: pontos megszakításkezelés Pontatlan megszakításkezelés Probléma: MUL ADD JZ 17.oldal Architektúrák II. - - Párhuzamos feldolgozás esetén várhatóan az ADD utasítás fejeződik be hamarabb, és lehet, hogy pl. túlcsordulással – amennyiben ezt a processzor elfogadja,

akkor az állapottere elveszti korrektséget, ami csak kiegészítő eljárásokkal lehet helyreállítani. Ennek oka, hogy a korábbi MUL utasítás még definiálatlan s így felborulhat a kivételkezelés soros konzisztenciája Pl.: Power1 (1990) és Power 2 (1993) – csak a lebegőpontos utasításoknál Az Alpha processzorok viszont minden utasításnál Pontos megszakításkezelés - A processzor kizárólag az eredeti utasítás szekvenciának megfelelő sorrendben fogadja el a megszakításkéréseket - Ehhez általában átrendező-puffert használ, így a processzor csak akkor fogadja el a megszakításkérést, amikor az adott utasítást kiírjuk az átrendező-pufferből. Pl: Az Intel processzorcsalád, és a mai processzorok - Az ILP processzorok gyorsítási lehetőségei, avagy a programban rejlő utasításszintű párhuzamossági lehetőségek Az utasításszintű párhuzamosítási lehetőségeket korlátozzák (adat-, vezérlés –és erőforrás f.)

Feltételezzük, hogy eltekinthetünk az erőforrás függőségektől, hogy a processzor regiszterátnevezéssel feloldja az ál adat-függőségeket A valódi adatfüggőséget és a vezérlésfüggőséget kell csak figyelembe venni Az irodalom megkülönbözteti az általános célú programokat (compiler-ek és a nem numerikus feldolgozások), valamint a tudományos célú programokat (lebegőpontos számítások) Az irodalom alapján az általános célú programoknál az ILP gyorsítási lehetőség kétszeres, a tudományos programoknál pedig kétszeres – négyszeres Magyarázat: a feltételes vezérlésátadások alapblokkokra bontják a programot, a párhuzamosítást o csak az alapblokkokon belül vizsgálják, s o az alapblokkok pedig tipikusan rövidek A programokban rejlő utasításszintű párhuzamosság kihasználása - kihasználjuk a ciklusokban rejlő párhuzamosságot o Erre többféle eljárás létezik, pl.: szoftver futószalag L L1 L1 L2 Ln Ciklus L2

Az n-szer kibontott ciklus párhuzamos végrehajtásra előkészítve Az összesített eredmények Ln Az n-szer kibontott ciklus Hátránya: pl.: két darab végrehajtóegység esetén csak maximum kétszeres gyorsítás érhető el, így csak az erőforrás-korláttól függ a gyorsítás mértéke. o A vezérlésfüggőségek problémaköre: Amennyiben 100%-osan meg tudnánk mondani előre a vezérlési utasítások irányát, akkor 10x-100x-os gyorsítást is el tudnánk érni Elvben a program minden ágát is feldolgozhatnánk, azonban csak kétirányú feldolgozásokat feltételezve N darab elágazás esetén 2N darab utat kellene bejárni, ami kezelhetetlenül sok. 18.oldal Architektúrák II. Ennek az elvnek a gyakorlatban használható vetületei: • Megbecsüljük a várható irányt. A feltétel kiértékelésekor o Amennyiben a becslés helyes volt, folytatódik a feldolgozás a megkezdett (helyes) irányba o Amennyiben viszont hibás, a rossz irányba

lehívott utasításokat eldobjuk, s elkezdjük az utasítások lehívását a helyes irányba • Mindkét irányba megindítjuk a feldolgozást, s a feltétel kiértékelése után, a rossz irányba lehívott utasításokat eldobjuk. Az utasításszintű párhuzamosság kihasználásával napjainkban: - általános célú programok esetén mintegy négyszeres, - tudományos műszaki programok esetén 10-20 szoros gyorsítás Időbeli párhuzamosság: futószalagos feldolgozás Fejlődése: - Előlehívás: Az előző utasítás visszaírási fázisát és az aktuális utasítás lehívási fázisát párhuzamosítjuk - o maximum egy óraciklus nyerhetünk, amit a függőségek mérsékelnek o Példa: A hatvanas évek nagyszámítógépeinek egy része A 8086-os mikroprocesszor Csak a végrehajtás fázisban (futószalag-elvű kialakítás): - - Példa: o Nagyszámítógépek: a 60-as évek vektorprocesszoros gépei Mikroszámítógépek: ez a fázis kimaradt A

teljes utasítás-feldolgozási fázisban o Maximum óraciklusonként tudunk feldolgozni egy utasítás, amit a függőségek mérsékelnek o Példa: Nagyszámítógépek (1960) Mikroszámítógépek: 80286 A futószalagos feldolgozás következményei Memóriakezelés: o A memória lassabb, mint a processzor. Hagyományos, szekvenciális elvű 4 ciklusú utasítás: Négyfokozatú futószalag esetén: 19.oldal Architektúrák II. - Míg a hagyományos szekvenciális feldolgozásnál – a példánk esetében – csak minden negyedik óraciklusban kell utasítást lehívni, addig 4 fokozatú futószalagnál már maximum óraciklusonként, amit a függőségek csökkenthetnek. o A memória-alrendszert gyorsításokkal egészítették ki o A gyorsítótárak a 80-as évek második felében terjedtek el robbanásszerűen, a futószalagos feldolgozás terjedésével párhuzamosan Vezérlés-függőségek: o Az okozott teljesítmény-redukció mértéke: Feltétlen

vezérlésátadás esetén az ugrási rés (buborék) mérete N-1, ahol N a futószalag fokozatainak száma Feltételes vezérlésátadás esetén ehhez hozzájön a feltétel kiértékelés, az ugrási cím számítása és a bonyolultabb dekódolás is o A teljesítmény-csökkenés mérséklése: A korai gépekben hardver-kiegészítéssel lehetővé tették, hogy a dekódolás végére előálljon az ugrási cím A korai RISC gépekben késleltetett ugrást alkalmaztak A CISC gépek esetén megjelent: • A fix előrejelzés: A következő végrehajtandó utasítás mindig az ugrási címen helyezkedik el • Az ugrási cím előáll a dekódolási szakasz végére, majd folytatják az utasítások lehívását az ugrási címet követően • A feltételes vezérlés-átadásokban a feltételek kiértékelése az execution szakasz végén következett be: o Az előrejelzés helyes volt s folytatódott az utasítások feldolgozása az elkezdett irányba o Hibás

volt, ekkor az elkezdett utasításokat eldobták és elkezdték a feldolgozást a helyes irányba. Pl: 80486 • Feloldatlan feltételes vezérlési függőség: amikor a feltétel nagy késleltetésű (látenciájú) (szorzás, osztás) utasításra vonatkozik, ami nem hajtódik végre a feltételes vezérlésátadási utasítás execution szakaszának végére ezért blokkolódik a feldolgozás. Pl.: a=x/y if a=1 (várnia kell az előzőre) A futószalagos feldolgozás jellemzői 1. A fokozatok száma: A függőségek miatt sok utasítást kell eldobni! - Pl.: 1980, RISC I. – kétfokozatú, 1982, RISC II – háromfokozatú, napjainkban 15 – 20 fokozat 2. Újrafeldolgozás Újrafeldolgozás nélkül: Újrafeldolgozással, pl.: szorzás, osztás esetén igen hosszú lenne, ha a részeredményeket műveletenként kimentenénk a regiszterekbe. Helyette a részeredményeket az E fokozat végéről visszavezetjük az E fokozat bemenetére. (elemi műveletek sorozata) 20.oldal

Architektúrák II. 3. Operandus-előrehozás 4. Szinkron – aszinkron: napjainkban szinkron az elterjedt A futószalag logikai felépítése 1. szint: A futószalagok funkcionális meghatározása pl.: 2. szint: az egyes fokozatok által végrehajtandó elemi műveletek pl.: Fetch MAR ← PC MDR ← (MAR) IR ← (MDR) PC ← PC+1 A futószalagok fizikai felépítése - általános fizikai felépítés 1960-80 90-es évek (itt jelenik meg a többszörözés): - fizikai megvalósítás: o Univerzális futószalag: minden logikai futószalagot egyetlen fizikai futószalagon valósítunk meg, Pl.: RISC I o Master futószalag (Pentium I.): Két futószalag közül: Az egyik minden utasítás végrehajtására alkalmas, A másik csak az egyszerűbb utasítások végrehajtására képes o Dedikált futószalag, pl.: ProwerPC 604 FX összetett: szorzás, osztás. Képes az újrafeldolgozásra 21.oldal Architektúrák II. Soros konzisztencia (CO): A konzisztencia